### Design and Implementation of the TRIPS EDGE Architecture

#### TRIPS Tutorial Originally Presented at ISCA-32 June 4, 2005

Department of Computer Sciences The University of Texas at Austin

### **Tutorial Outline**

#### • Part I: Overview

- Introduction (*Doug Burger/Steve Keckler*)

- EDGE architectures and the TRIPS ISA (*Doug Burger*)

- TRIPS microarchitecture and prototype overview (*Steve Keckler*)

- TRIPS code examples (*Robert McDonald*)

#### • Part II: TRIPS Front End

- Global control (*Ramdas Nagarajan*)

- Control-flow prediction (*Nitya Ranganathan*)

- Instruction fetch (*Haiming Liu*)

- Register accesses and operand routing (*Karu Sankaralingam*)

- Part III: TRIPS Execution Core & Memory System

- Issue logic and execution (*Premkishore Shivakumar*)

- Primary memory system (*Simha Sethumadhavan*)

- Secondary memory system (*Changkyu Kim*)

- Chip- and system-level networks and I/O (*Paul Gratz*)

- Part IV: TRIPS Compiler

- Compiler overview (Kathryn McKinley)

- Forming TRIPS Blocks (*Aaron Smith*)

- Code optimization (*Kathryn McKinley*)

- Part V: Conclusions

Names in italics refer to both the presenters at ISCA-32 and the main developers of each section's slide deck.

•

# **Copyright Information**

- The material in this tutorial is Copyright © 2005-2006 by The University of Texas at Austin. All rights reserved.

- This material was developed as a part of the TRIPS project in the Computer Architecture and Technology Laboratory, Department of Computer Sciences, at The University of Texas at Austin. Please contact Doug Burger (<u>dburger@cs.utexas.edu</u>) or Steve Keckler (<u>skeckler@cs.utexas.edu</u>) for information about redistribution or usage of these materials in other presentations.

- Portions of the TRIPS technology described in this tutorial are patent pending. Commercial parties interested in licensing or using TRIPS technology for profit should contact the project principal investigators listed above.

### Acknowledgment of TRIPS Sponsors

**PCA**

inte

- DARPA

- Polymorphous Computing Architectures (2001-2006)

- Contracts F33615-01-C-1892 and F44615-03-C-4106

- Special thanks to Bob Graybill

- Air Force Research Laboratory

- Intel Research Council

- 2 Research Grants (2000-2004) and equipment donations (2000-2005)

- IBM

- Sun Microsystems

- Research Grant (2003)

- National Science Foundation

- CAREER and Research Infrastructure Grants (1999-2008)

- Peter O'Donnell Foundation

- UT-Austin College of Natural Sciences

- Matching funds for industrial fellows, infrastructure grants (1999-2008)

#### Other Members of the TRIPS Team

#### Research Scientists

- Bill Yoder

- Chief developer of the TRIPS toolchain

- Jim Burrill

- Chief engineer of the Scale compiler

- Nick Nethercote

- TRIPS compiler performance leader

#### Graduate Students

- Xia Chen

- PowerPC to TRIPS translation and emulation

- Raj Desikan

- Initial data tile design

- Saurabh Drolia

- Prototype DMA controller, system simulator, parallel software

- Madhu Sibi Govindan

- Prototype external bus and clock controller

- Divya Gulati

- Execution tile design, processor core verification

- Heather Hanson

- Operand router design

- Sundeep Kushwaha

- Back-end instruction placement

- Bert Maher

- Hyperblock construction and formation

- Suriya Narayanan

- Compiler/memory system optimization

- Sadia Sharif

- TRIPS system software

### Relevant TRIPS/EDGE Publications

- "The Design and Implementation of the TRIPS Prototype Chip"

- HotChips 17, 2005.

- Contains details about the prototype ASIC.

- "Dynamic Placement, Static Issue (SPDI) Scheduling for EDGE Architectures"

- Intl. Conference on Parallel Architectures and Compilation Techniques (PACT), 2004.

- Specifies compiler algorithm for scheduling instructions on the TRIPS architecture.

- "Scaling to the End of Silicon with EDGE Architectures"

- IEEE Computer, July, 2004

- Provides an overview of EDGE architectures using the TRIPS architecture as a case study.

- "Exploiting ILP, TLP, and DLP with the Polymorphous TRIPS Architecture"

- Intl. Symposium on Computer Architecture (ISCA-30), 2003.

- Details the flexibility of the TRIPS architecture for exploiting different types of parallelism.

- "An Adaptive, Non-Uniform Cache Structure for Wire-Dominated On-Chip Caches"

- Intl. Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS-X), 2002.

- The first paper describing NUCA caches and their design tradeoffs.

- "A Design Space Evaluation of Grid Processor Architectures"

- Intl. Symposium on Microarchitecture (MICRO-34), 2001.

- An early study that formed the basis for the TRIPS architecture.

### Principal Related Work

- Transport-Triggered Architectures [Supercomputing 1991]

- Hans Mulder and Henk Corporaal

- MOVE Architecture had direct instruction-to-instruction communication bypassing registers

- WaveScalar [Micro 2003]

- Mark Oskin, Steve Swanson, Ken Michelson, and Andrew Schwerin

- Imperative/dataflow EDGE ISA

- 3 most significant differences with TRIPS:

- Dynamic instruction placement

- All-path execution

- Two-level microarchitectural execution hierarchy

- ASH/CASH/Pegasus IR [CGO-03, ASPLOS-04, ISPASS-05]

- Mihai Budiu and Seth Goldstein

- Similar goals and related compiler techniques

- More of a focus on compiling to ASICs or reconfigurable substrates

- RAW [IEEE Computer-97, ISCA-04]

- Pioneering tiled architecture tackling concurrency and wire delays

- Leading work on Scalar Operand Networks

- Direct instruction-to-instruction communication through network switch I-stream

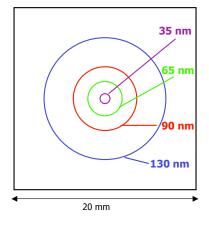

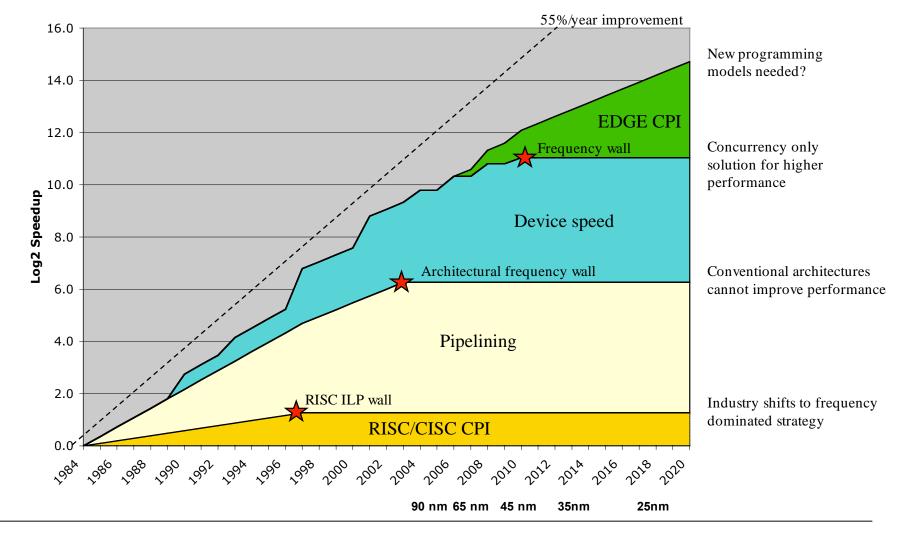

# Key Trends

- Power

- Now a budget, just like area

- What performance can you get for a given power and area budget?

- Transferring work from the HW to the SW (compiler, programmer, etc.) is power efficient

- Leakage trends must be addressed (not underlying goal of TRIPS)

- Slowing (stopping?) frequency increases

- Pipelining has reached depth limits

- Device speed scaling may stop tracking feature size reduction

- May result in decreasing main memory latencies

- Must exploit more concurrency

- Key issue: how to expose this concurrency? Force the programmer?

- Wire Delays

- Will force growing partitioning of future chips

- Works against reduced power and improved concurrency

- Reliability

- Do everything twice (or thrice) at some level of abstraction

- Works against power limits and exploitation of concurrency

### Performance Scaling and Technology Challenges

Single-processor Performance Scaling

June 4, 2005

**UT-Austin TRIPS Tutorial**

#### EDGE Architectures: Can New ISAs Help?

## The TRIPS EDGE ISA

#### **ISCA-32** Tutorial

Doug Burger

Department of Computer Sciences The University of Texas at Austin

### What is an EDGE Architecture?

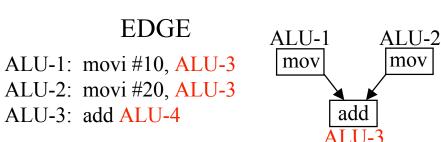

#### • Explicit Data Graph Execution

- Defined by two key features

- 1. Program graph is broken into sequences of *blocks*

- Basic blocks, hyperblocks, or something else

- Blocks commit atomically or not a block never partially executes

- 2. Within a block, ISA support for direct producer-to-consumer communication

- No shared named registers within a block (point-to-point dataflow edges only)

- Caveat: memory is still a shared namespace

- The block's dataflow graph (DFG) is explicit in the architecture

- What are design alternatives for different architectures?

- Single path through program block graph (TRIPS)

- All paths through program block graph (WaveScalar)

- Mechanism for specifying instruction-to-instruction links in the ISA

- Block constraints (composition, fixed size vs. variable size, etc.)

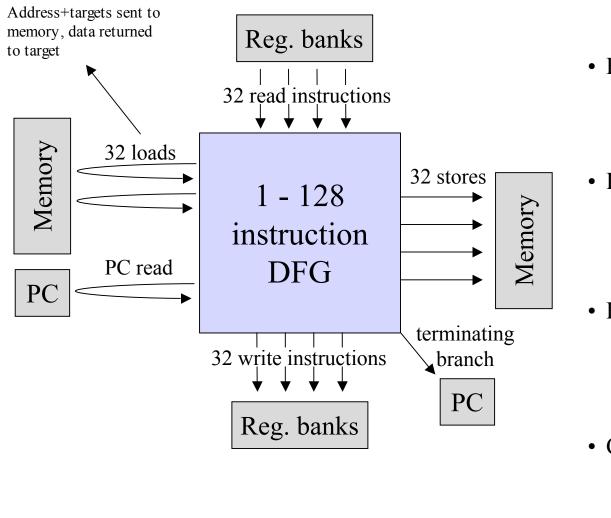

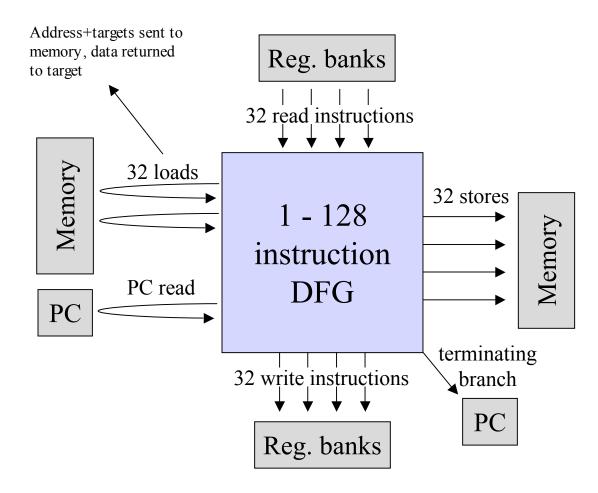

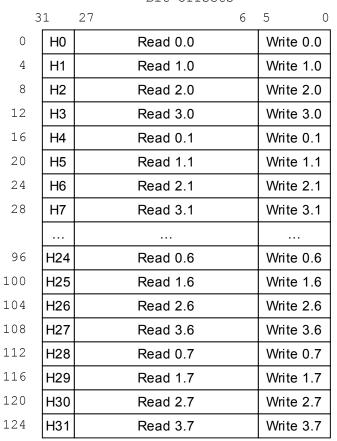

#### Architectural Structure of a TRIPS Block

#### **Block characteristics**:

- Fixed size:

- 128 instructions max

- L1 and core expands empty 32-inst chunks to NOPs

- Load/store IDs:

- Maximum of 32 loads+stores may be emitted, but blocks can hold more than 32

- Registers:

- 8 *read insts*. max to reg.

bank (4 banks = max of 32)

- 8 write insts. max to reg bank (4 banks = max of 32)

- Control flow:

- Exactly one branch emitted

- Blocks may hold more

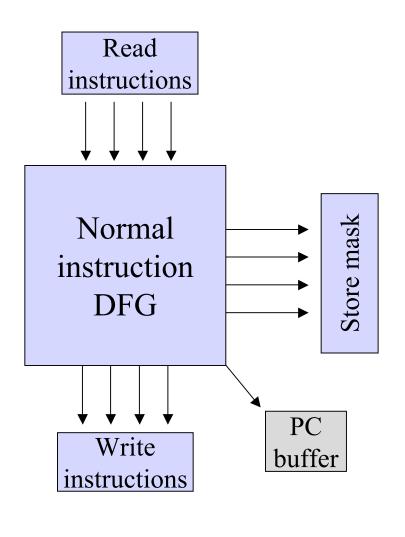

### **TRIPS Block Contents**

#### Blocks encoded in object file include:

- Read/Write instructions

- Computation instructions

- 32-bit store mask for tracking store completion

#### Two major considerations

- Every possible execution of a given block must emit a consistent number of outputs (register writes, stores, PC)

- Outputs may be actual or null

- Different blocks may have different #s of outputs

- No block state may be written until block is committed

- Bulk commit is logically atomic

- Similar to an architectural checkpoint in some respects

#### **TRIPS Block Example**

#### **RISC code**

TIL (operand format)

TASL (target format)

| ld   | R3, | 4(R2)  |

|------|-----|--------|

| add  | R4, | R1, R3 |

| st   | R4, | 4(R2)  |

| addi | R5, | R4, #2 |

| beqz | R4, | Block3 |

|      |     |        |

- Read target format

- Predicated instructions

- LD/ST sequence numbers

- Target fanout with movs

- Block outputs fixed (3 in this example)

| .bbegin   | bloc} | <1         |

|-----------|-------|------------|

| read      | \$t1, | \$g1       |

| read      | \$t2, | \$g2       |

| ld        | \$t3, | 4(\$t2)    |

| add       | \$t4, | \$t1, \$t3 |

| st        | \$t4, | 4(\$t2)    |

| addi      | \$t5, | \$t4, 2    |

| teqz      | \$t6, | \$t4       |

| b_t<\$t6> | bloc} | x3         |

| b_f<\$t6> | bloc} | <2         |

| write     | \$g5, | \$t5       |

| .bend     | bloc} | <1         |

|           |       |            |

| .bbegin   | blocł | <2         |

| [R1]<br>[R2]<br>[1] | -    | [2]<br>[1] [4]<br>L[1] 4 [2] |

|---------------------|------|------------------------------|

| [2]                 | add  | [3] [4]                      |

| [3]                 | mov  | [5] [6]                      |

| [4]                 | st   | S[2] 4                       |

| [5]                 | addi | 2 [W1]                       |

| [6]                 | teqz | [7] [8]                      |

| [7]                 | b_t  | block3                       |

| [8]                 | b_f  | block2                       |

| [W1]                | \$g5 |                              |

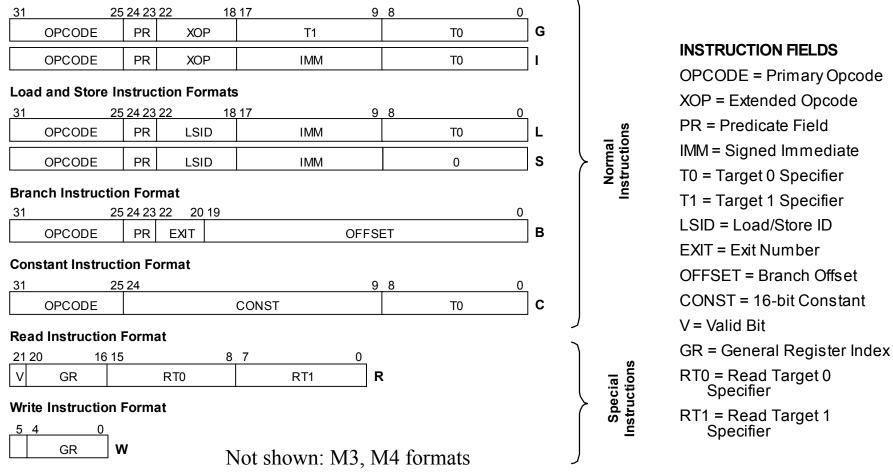

## Key Features of TRIPS ISA

- Fixed instruction lengths all instructions 32 bits

- Read and write instructions

- Contained in block header for managing DFG/register file communication

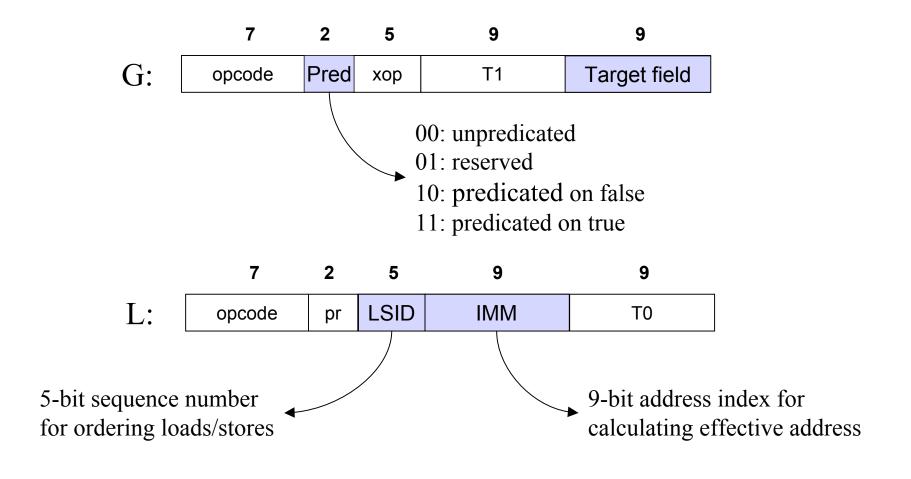

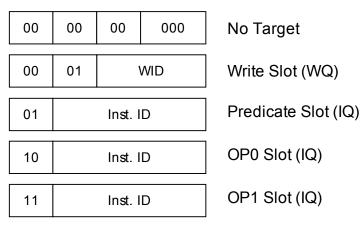

- Target format (T0, T1)

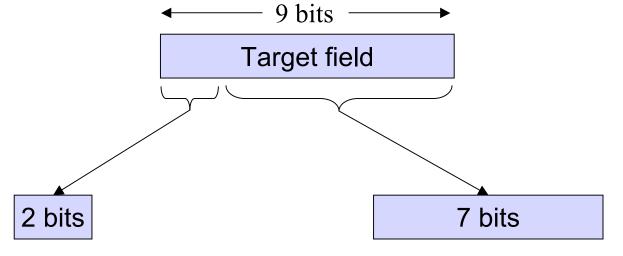

- Output destinations specified with 9-bit targets

- Predication (PR)

- Nearly every instruction has a predicate field, encoded for efficient dataflow predication

- Load/store IDs (LSID)

- Used to maintain sequential memory semantics despite EDGE ISA

- Exit bits (EXIT)

- Used to improve block exit control prediction

#### **TRIPS** Instruction Formats

#### **General Instruction Formats**

### TRIPS G and L formats

## Target (Operand) Formats

- 00: No target (or write inst.)

- 01: Targets predicate field

- 10: Targets left operand

- 11: Targets right operand

- Names one of 128 target instructions

- Location of instruction is microarchitecture dependent

01 5 bits

• Names one of 32 write instructions

### Object Code Example

#### TASL (target format)

#### **Object Code**

| [R1] | \$g1 | [2]     |  |  |  |

|------|------|---------|--|--|--|

| [R2] | \$g2 | [1] [4] |  |  |  |

| [1]  | ld   | L[1] 4  |  |  |  |

| [2]  | add  | [3] [4] |  |  |  |

| [3]  | mov  | [5] [6] |  |  |  |

| [4]  | st   | S[2] 4  |  |  |  |

| [5]  | addi | 2 [W1]  |  |  |  |

| [6]  | teqz | [7] [8] |  |  |  |

| [7]  | b_t  | block3  |  |  |  |

| [8]  | b_f  | block2  |  |  |  |

| [W1] | \$g5 |         |  |  |  |

| v reg  | T  | 1    | ТО   | ]  |

|--------|----|------|------|----|

| v reg  | Т  | 1    | ТО   | ]  |

| opcode | pr | LSID | imm  | ТО |

| opcode | pr | хор  | T1   | Т0 |

| opcode | pr | хор  | T1   | ТО |

| opcode | pr | LSID | imm  | 0  |

| opcode | pr | хор  | imm  | ТО |

| opcode | pr | хор  | T1   | ТО |

| opcode | pr | exit | offs | et |

| opcode | pr | exit | offs | et |

| v reg  |    |      |      |    |

## Object Code Example

#### TASL (target format)

#### **Object** Code

| [R1] | \$g1 | [2]     |

|------|------|---------|

| [R2] | \$g2 | [1] [4] |

| [1]  | ld   | L[1] 4  |

| [2]  | add  | [3] [4] |

| [3]  | mov  | [5] [6] |

| [4]  | st   | S[2] 4  |

| [5]  | addi | 2 [W1]  |

| [6]  | teqz | [7] [8] |

| [7]  | b_t  | block3  |

| [8]  | b_f  | block2  |

| [W1] | \$g5 |         |

| 1 00001 | [2     | ]     |        |      |  |  |

|---------|--------|-------|--------|------|--|--|

| 1 00010 | [1     | ]     | [4]    |      |  |  |

| ld      | 00     | 00001 | 4      | [2]  |  |  |

| add     | 00     |       | [3]    | [4]  |  |  |

| mov     | 00     |       | [5]    | [6]  |  |  |

| st      | 00     | 00010 | 4      |      |  |  |

| addi    | 00     |       | 2      | [W1] |  |  |

| teqz    | 00     |       | [7]    | [8]  |  |  |

| b       | 11 (t) | E0    | block3 | - PC |  |  |

| b       | 10 (f) | E1    | block2 | - PC |  |  |

| 1 00101 |        |       |        |      |  |  |

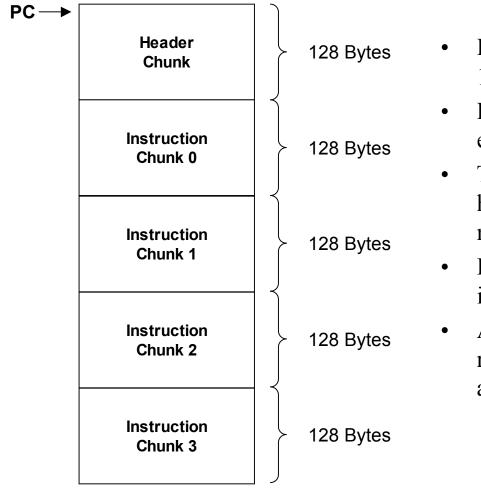

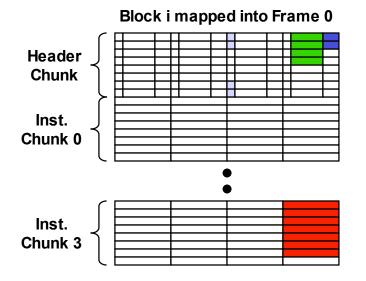

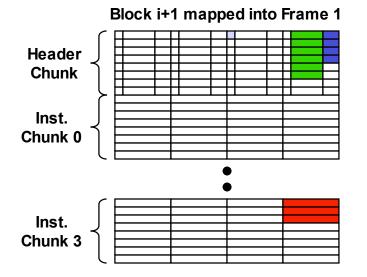

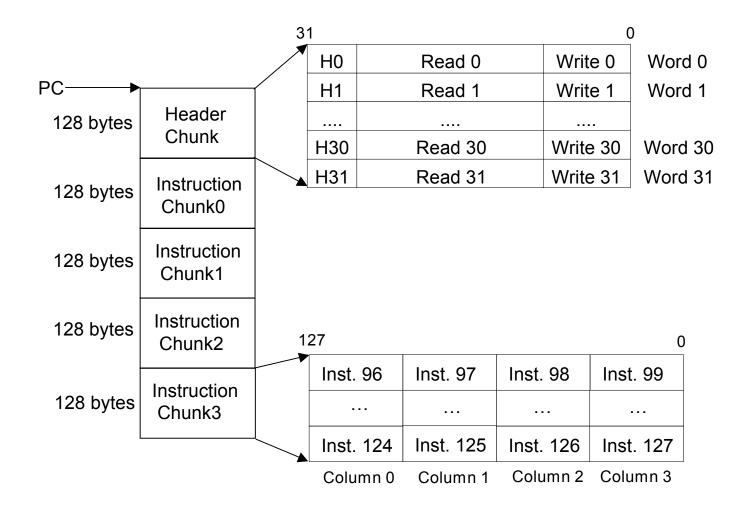

### **TRIPS Block Format**

- Each block is formed from two to five 128-byte program"chunks"

- Blocks with fewer than five chunks are expanded to five chunks in the L1 I-cache

- The header chunk includes a block header (execution flags plus a store mask) and register read/write instructions

- Each instruction chunk holds 32 4-byte instructions (including NOPs)

- A maximally sized block contains 128 regular instructions, 32 read instructions, and 32 write instructions

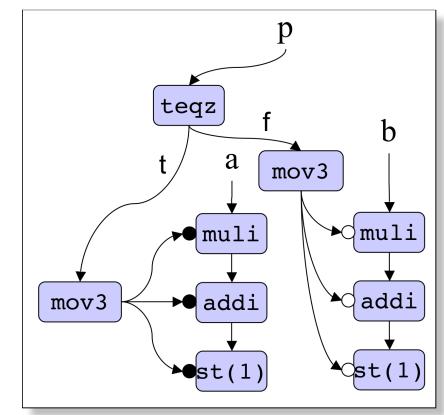

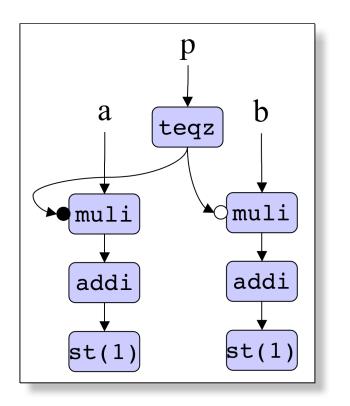

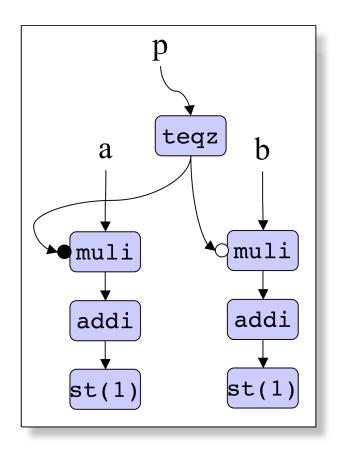

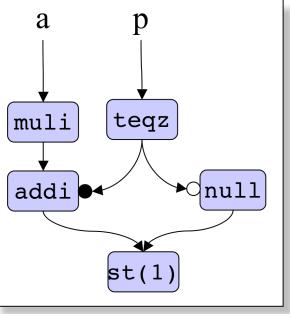

### Example of Predicate Operation

- Test instructions output low-order bit of 1 or 0 (T or F)

- Predicated instructions either match the arriving predicate or not

- An ADD with PR=10 is predicated on false, an arriving 0 predicate will match and enable the ADD

- Predicated instructions must receive all operands and a matching predicate before firing

- Instructions may receive multiple predicate operands but at most one matching predicate

- Despite predicates, blocks must produce fixed # of outputs.

#### Predicate Optimization and Fanout Reduction

- Predicate dependence heads ullet

- Reduce instructions executed

- Reduces dynamic energy by using less speculation

- Predicate dependence tails

- Tolerate predicate latencies with speculatively executed insts.

- Cannot speculate on block outputs

b

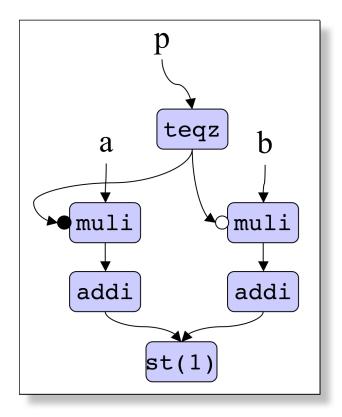

### Instruction (Store) Merging

• Old: two copies of stores down distinct predicate paths

- New: merge redundant insts.

- Speculative copies unneeded

- Only one data source will fire

## Nullified Outputs

- Each transmitted operand tagged with "null" and "exception" tokens.

- Nullified operands arriving at insts. produce nullified outputs

- Nulls used to indicate that a block won't produce a certain output (writes and stores)

Block with store down one conditional path:

. . .

## Exception Handling

- TRIPS exception types:

- fetch, breakpoint, timeout, execute, store, system call, reset, interrupt

- TRIPS exception model demands

- Must not raise exceptions for speculative instructions

- Key concept: propagate exception tokens within dataflow graph

- Instructions with exception-set operands do not execute, but propagate exception token to their targets

- Exceptions are detected at commit time if one or more block output (write, store, branch) has exception bit set

- Exceptions serviced between blocks

- "Block-precise" exception model

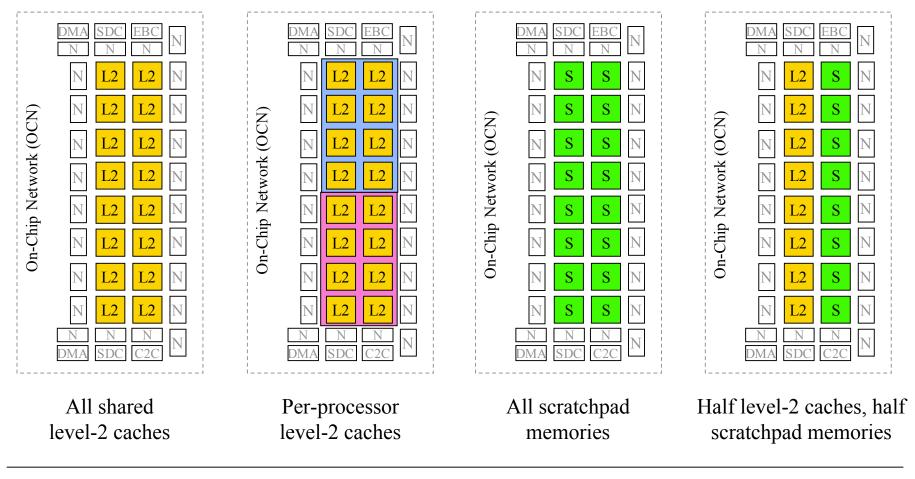

#### Other Architecturally Supported Features

- Execution mode via Thread Control Register

- Types of speculation (load, branch)

- Number of blocks in flight

- Breakpoints before/after blocks execute

- T-Morph via Processor Control Register

- Can place processors into single or 4-threaded SMT modes

- Per-bank cache/scratchpad configurations

- TLBs managed by software

- On-chip network routing tables programmed by software

- 40-bit global system memory address space

- Divided into SRF, cached memory, configuration quadrants

#### **TRIPS** Microarchitecture and Implementation

#### **ISCA-32** Tutorial

Steve Keckler

Department of Computer Sciences The University of Texas at Austin

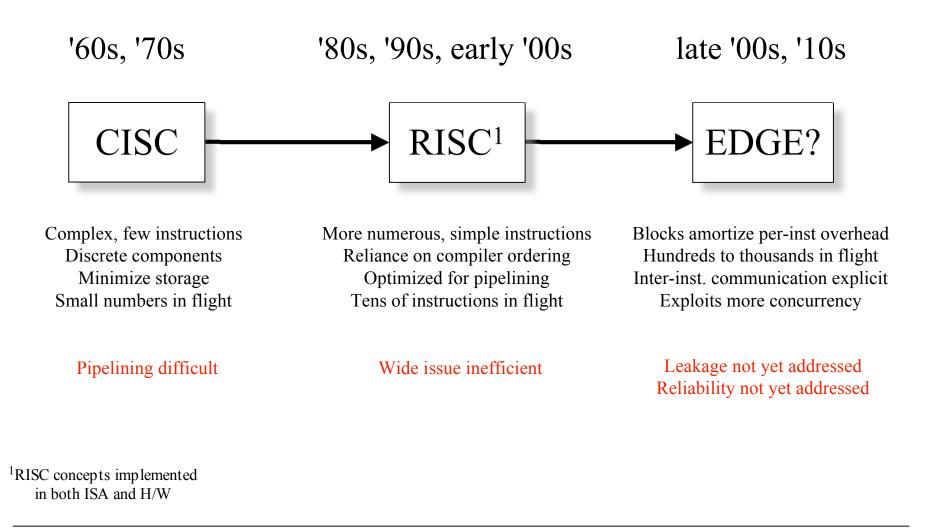

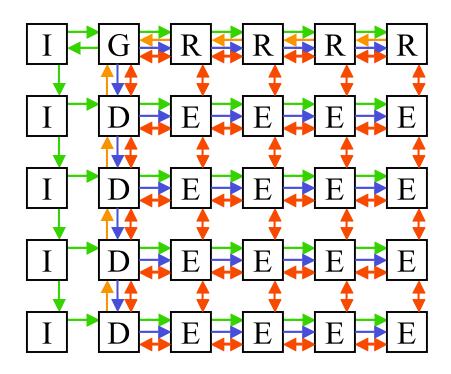

## **TRIPS** Microarchitecture Principles

- Limit wire lengths

- Architecture is partitioned and distributed

- Microarchitecture composed of different types of tiles

- No centralized resources

- Local wires are short

- Tiles are small (2-5 mm<sup>2</sup> per tile is typical)

- No global wires

- Networks connect only nearest neighbors

- Design for scalability

- Design productivity by replicating tiles (design reuse)

- Tiles interact through well-defined control and data networks

- Networks are extensible, even late in the design cycle

- Opportunity for asynchronous interfaces

- Prototype: employs communication latencies of 35nm technology, even though prototype is implemented in 130nm

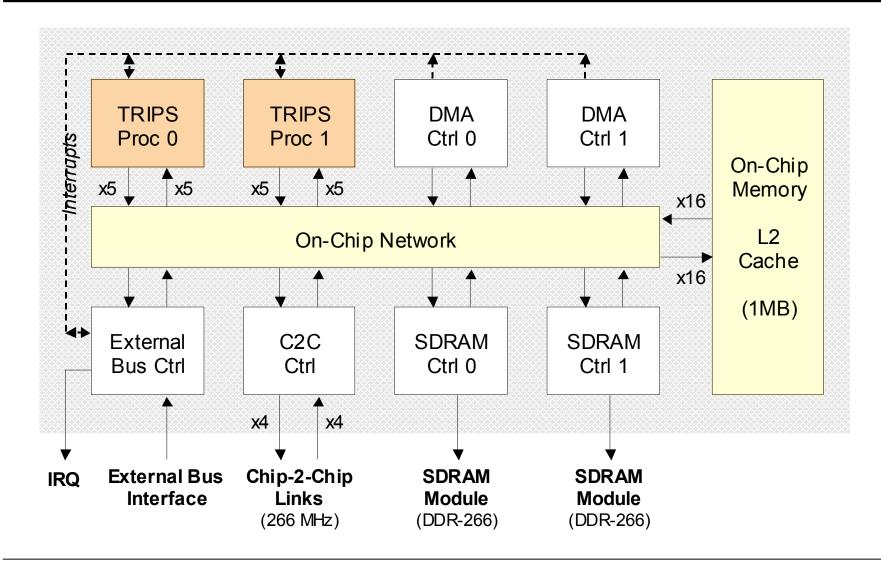

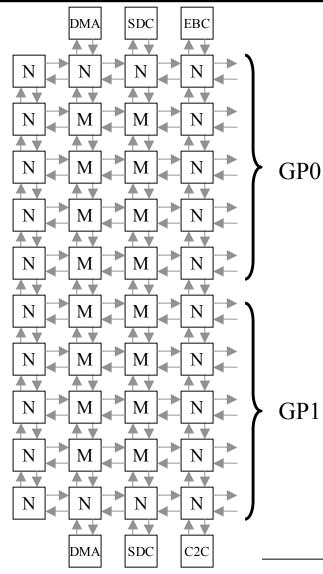

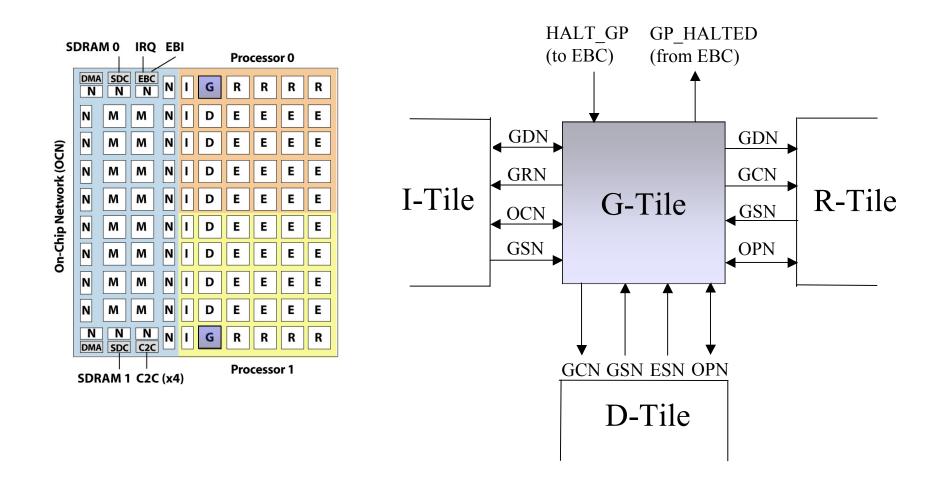

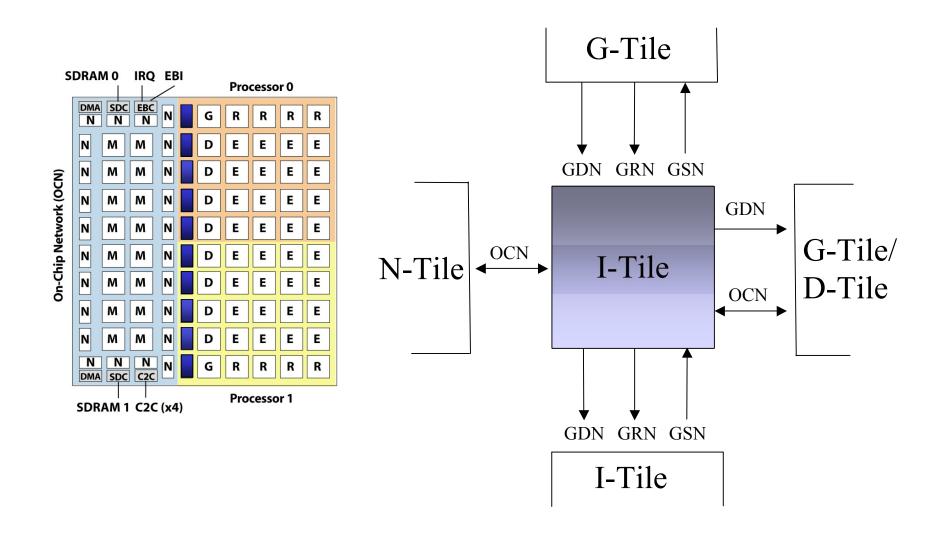

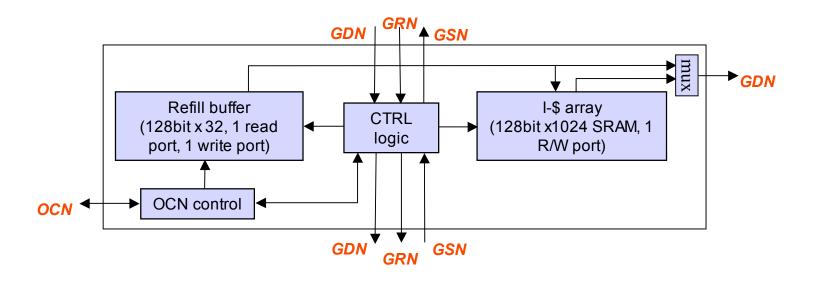

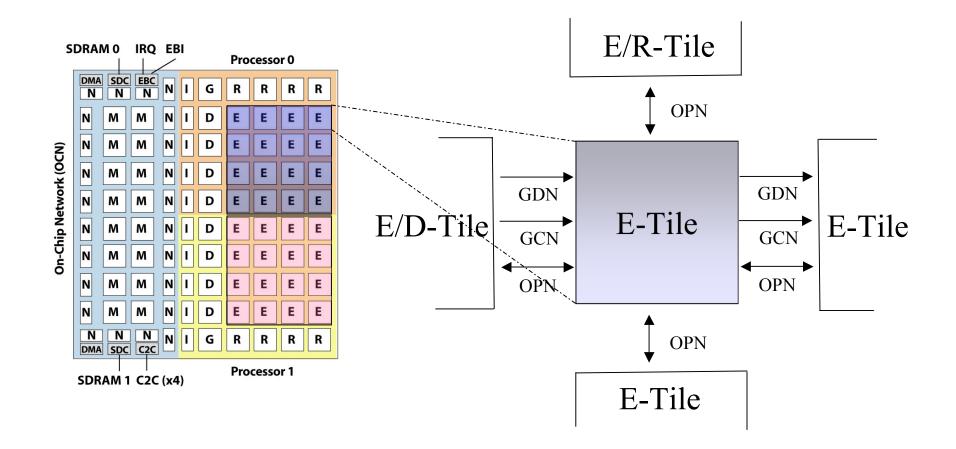

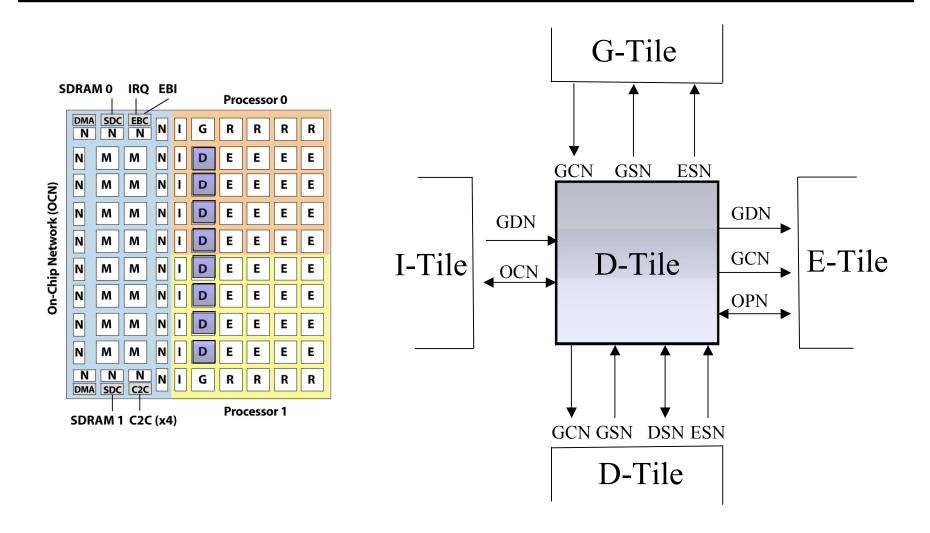

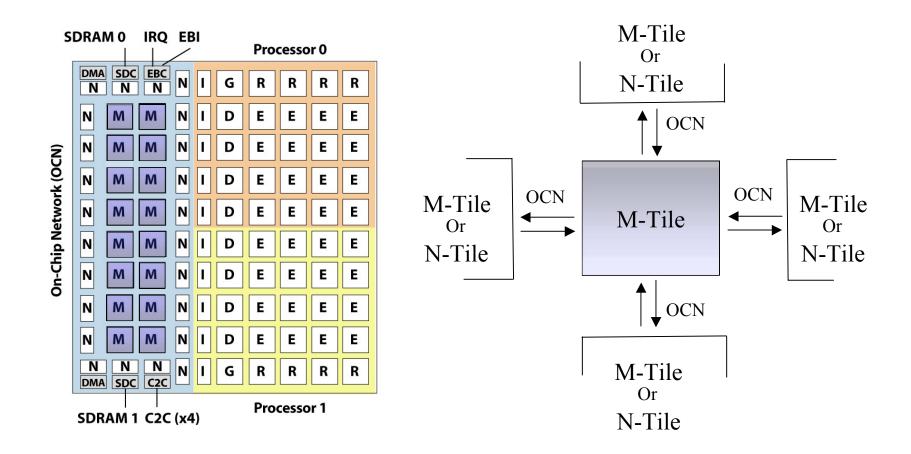

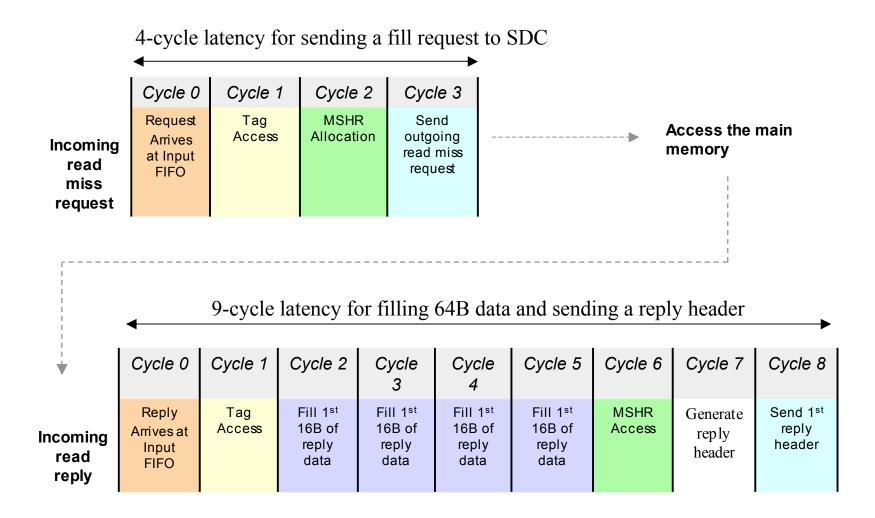

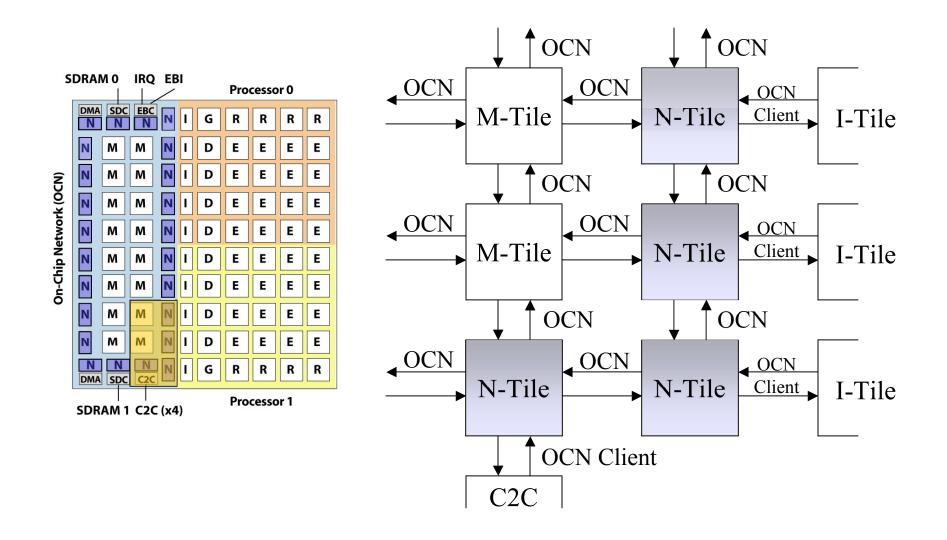

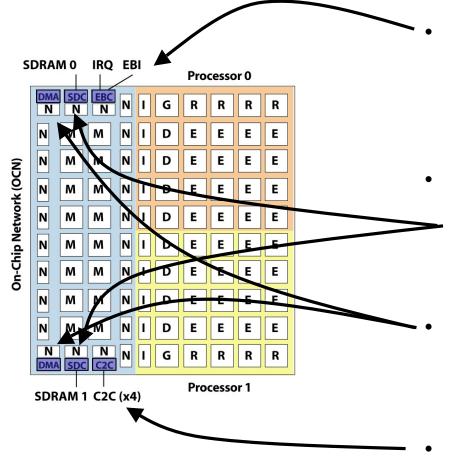

# **TRIPS** Chip Block Diagram

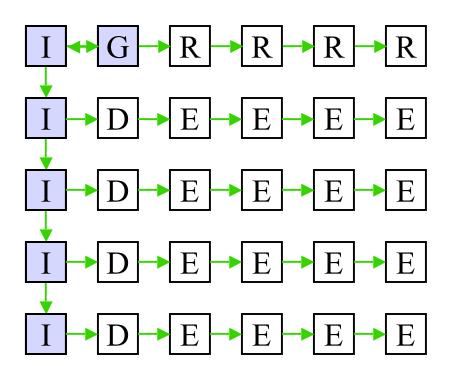

#### **TRIPS** Tile-level Microarchitecture

| SDRAM 0 IRQ EBI Processor 0 |                              |          |          |        |   |   | or O |   |   |   |

|-----------------------------|------------------------------|----------|----------|--------|---|---|------|---|---|---|

|                             | DMA<br>N                     | SDC<br>N | EBC      | ]<br>N | Ι | G | R    | R | R | R |

|                             | Ν                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

| î                           | Ν                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

| k (o                        | Ν                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

| On-Chip Network (OCN)       | Ν                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

| ip Ne                       | N                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

| n-Ch                        | Ν                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

| 0                           | Ν                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

|                             | N                            | Μ        | Μ        | Ν      | Ι | D | E    | E | E | E |

|                             | N<br>DMA                     | N<br>SDC | N<br>C2C | N      | Ι | G | R    | R | R | R |

| I                           | SDRAM 1 C2C (x4) Processor 1 |          |          |        |   |   |      |   |   |   |

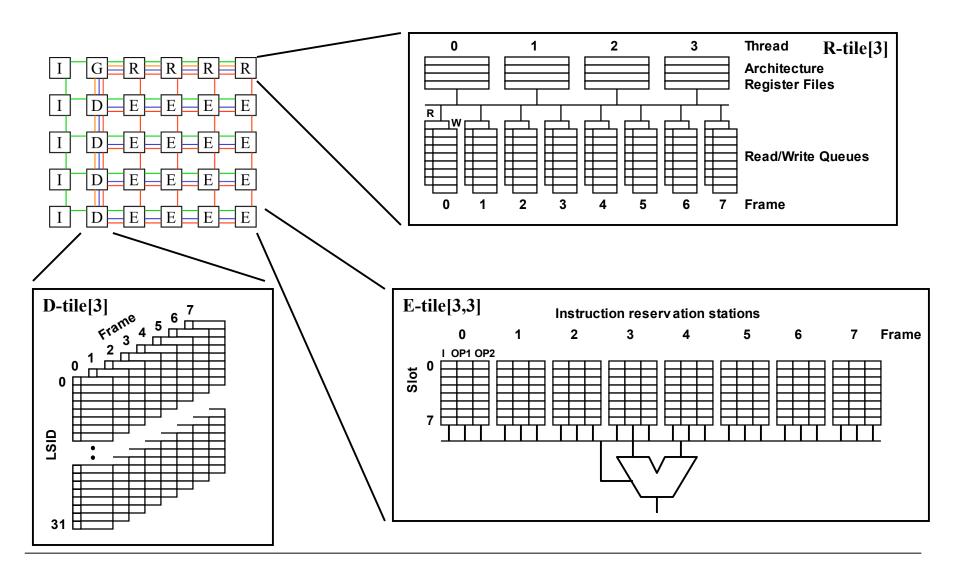

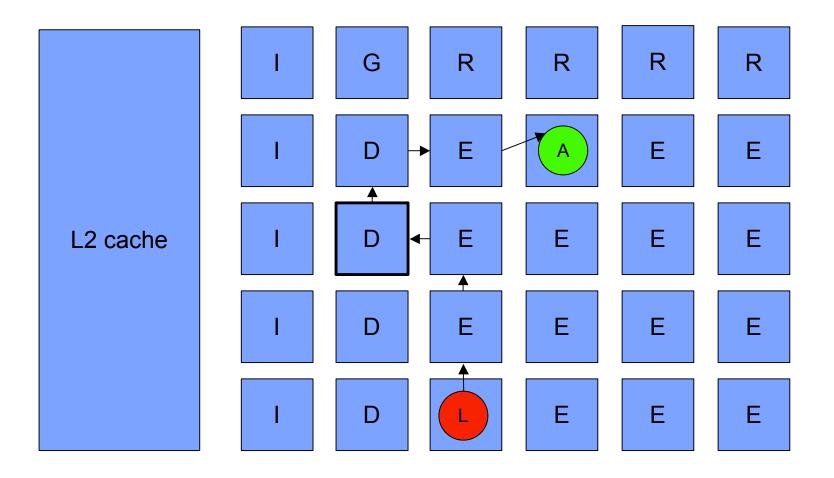

#### **TRIPS** Tiles

- G: Processor control TLB w/ variable size pages, dispatch, next block predict, commit

- R: Register file 32 registers x4 threads, register forwarding

- I: Instruction cache 16KB storage per tile

- D: Data cache 8KB per tile, 256-entry load/store queue, TLB

- E: Execution unit Int/FP ALUs, 64 reservation stations

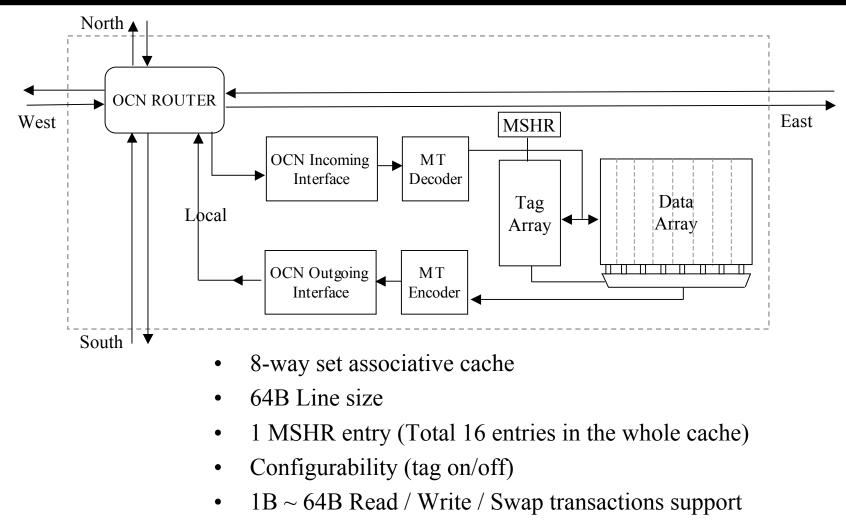

M: Memory - 64KB, configurable as L2 cache or scratchpad

- N: OCN network interface router, translation tables

- DMA: Direct memory access controller

- SDC: DDR SDRAM controller

- EBC: External bus controller interface to external PowerPC

- C2C: Chip-to-chip network controller 4 links to XY neighbors

#### Grid Processor Tiles and Interfaces

- GDN: global dispatch network

- **OPN**: operand network

- GSN: global status network

- GCN: global control network

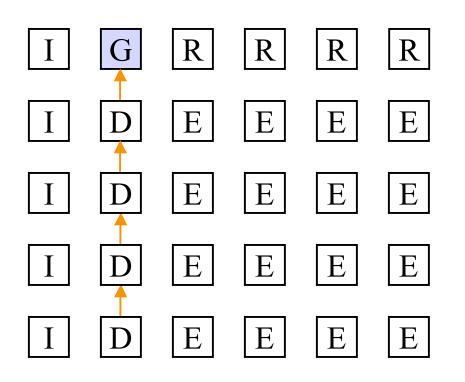

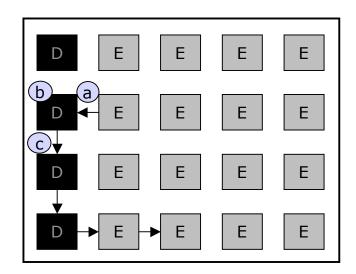

### Mapping TRIPS Blocks to the Microarchitecture

## Mapping TRIPS Blocks to the Microarchitecture

June 4, 2005

## Mapping TRIPS Blocks to the Microarchitecture

#### June 4, 2005

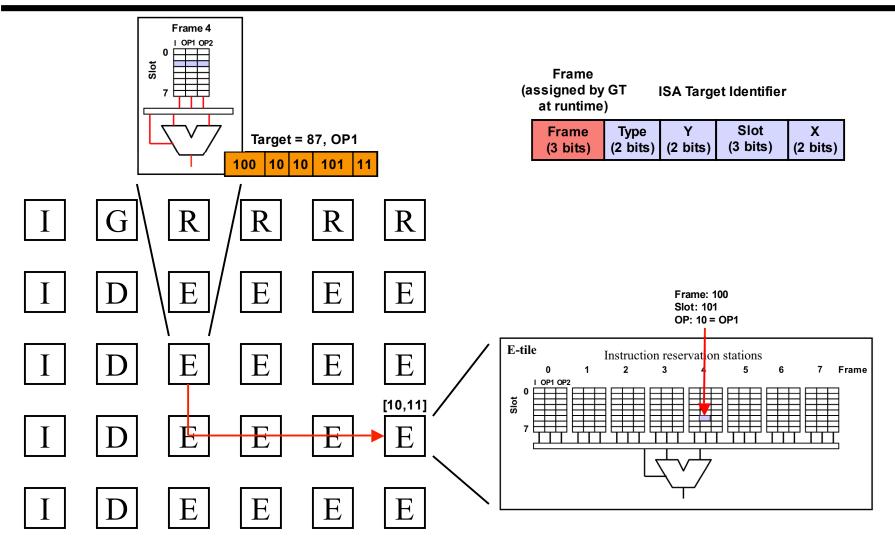

## Mapping Target Identifiers to Reservation Stations

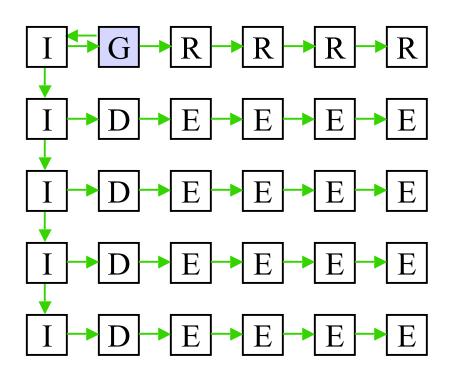

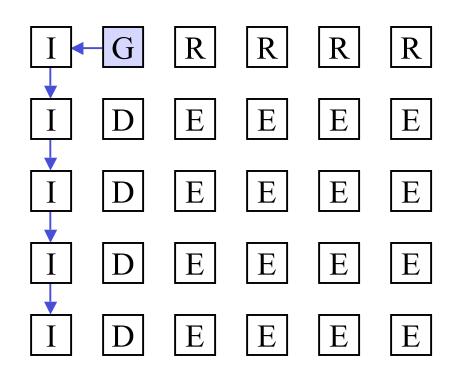

### Processor Core Tiles and Interfaces

- Fetch

- G-tile examines I\$ tags

- Sends dispatch command to I-tiles

- I-tiles fetch instructions, distribute to R-tiles, E-tiles

### Processor Core Tiles and Interfaces

- Execute

- R-tiles inject register values

- E-tiles execute block instructions

- compute, load/store

- E-tiles delivers outputs

- Results to R-tiles/D-tiles

- Branch to G-tile

### Processor Core Tiles and Interfaces

- Commit

- R-tiles/D-tiles accumulate outputs

- Send completion messages to G-tile

- G-tile sends commit message

- R-tiles/D-tiles respond with commit acknowledge

- R-tiles commit state to register files

- D-tiles commit state to data cache

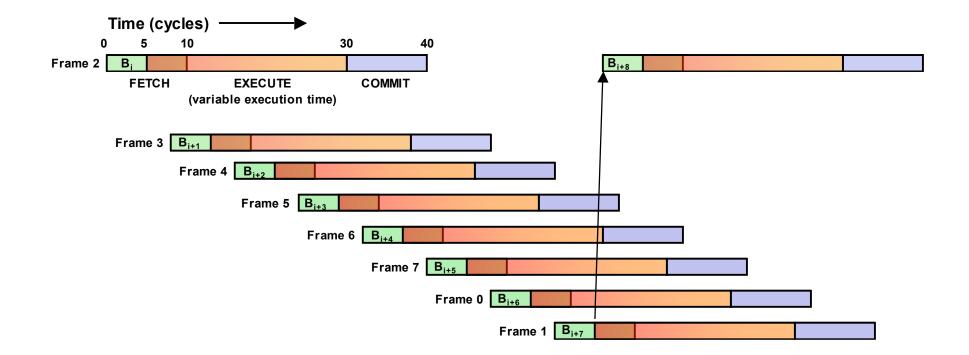

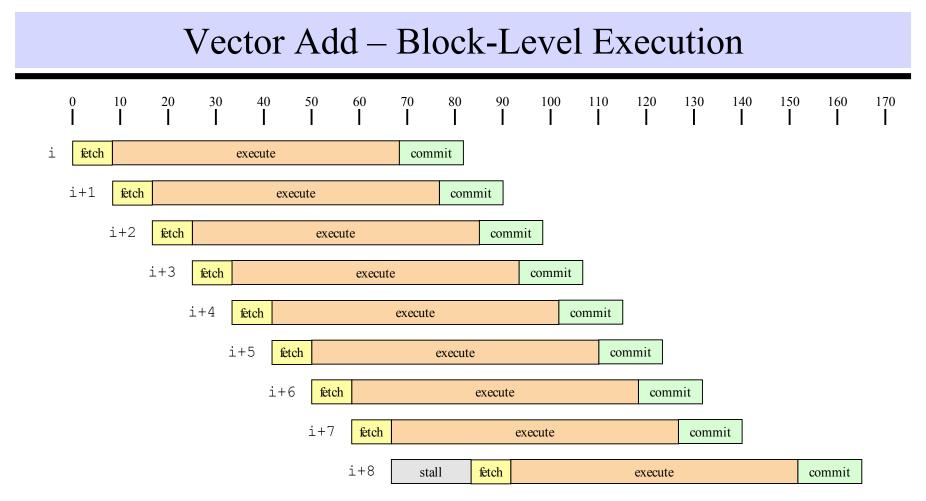

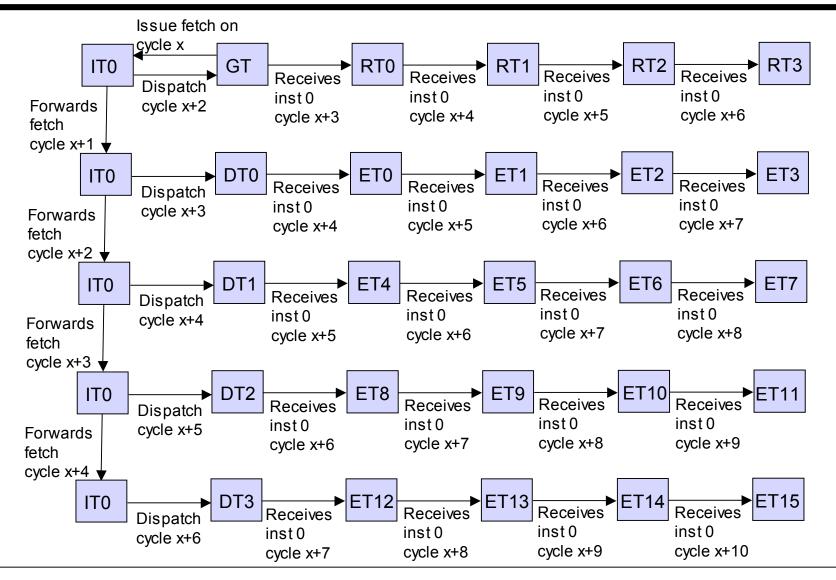

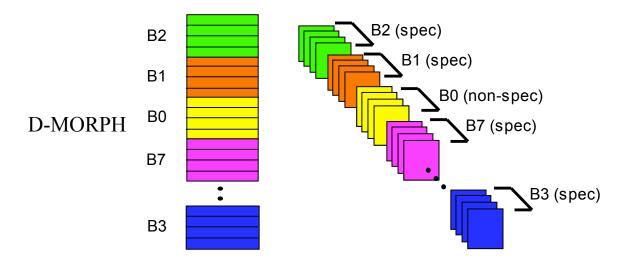

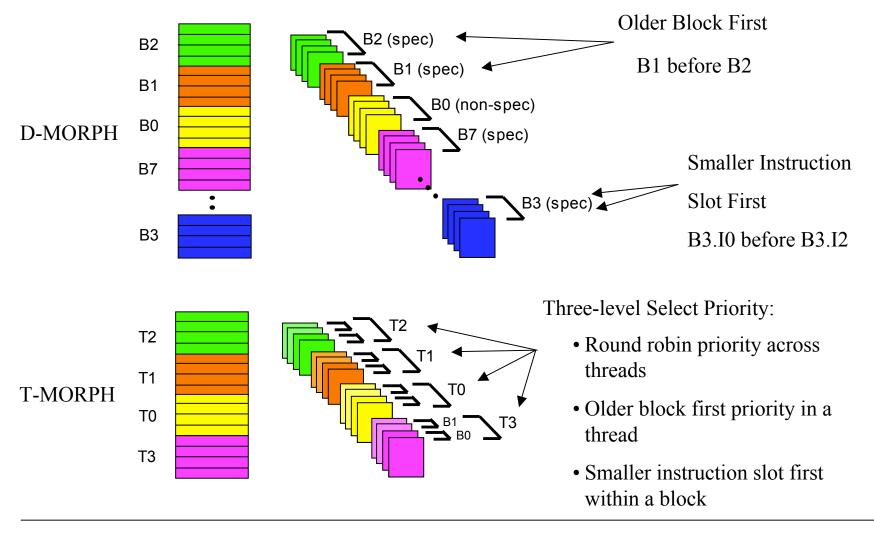

## **Block Execution Timeline**

- Execute/commit overlapped across multiple blocks

- G-tile manages frames as a circular buffer

- D-morph: 1 thread, 8 frames

- T-morph: up to 4 threads, 2 frames each

## **On-Chip** Network

- Flexible/fast on-chip network fabric

- Programmable translation tables

- Configurable 1 MB memory system

- 128-bit wide, 533 MHz

- 6.8GB/sec per link

- M-tile (on-chip memory)

- 64 KB SRAM capacity

- Configurable tag array (on/off)

- N-tile with translation tables

- System address  $\Rightarrow$  OCN address

- EBC external bus controller

- Connection to master control processor

- SDC DDR1 SDRAM controller

- 1.1 GB/sec per controller

- DMA controller

- Linear, scatter-gather, chaining

June 4, 2005

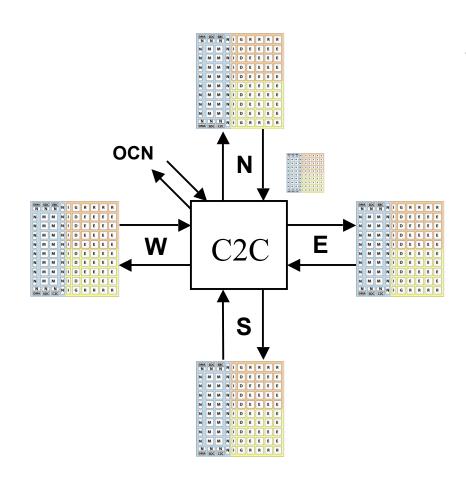

### Chip-to-Chip (C2C) Network

- Glueless interchip network

- Extension of OCN

- 2D mesh router

- 64-bits wide

- 266MHz,1.7GB/sec per link

## Chip Implementation

- Chip Specs

- 130 nm 7LM IBM ASIC process

- 18.3mm x 18.3mm die

- 853 signal I/Os

- 568 for C2C

- 216 for SDCs

- $\sim 70 \text{ misc I/Os}$

- Schedule

- 5/99: Seed of TRIPS ideas

- 12/01: Publish TRIPS concept architecture

- 10/02: Publish NUCA concept architecture

- 6/03: Start high-level prototype design

- 10/03: Start RTL design

- 2/05: RTL 90% complete

- 7/05: Design 100% complete

- 9/05: Tapeout

- 12/05: Start system evaluation in lab

|        | OCN + controllers |             |     |      | GP0         |             |      |     |       |        |                  |     |          |     |      |     |

|--------|-------------------|-------------|-----|------|-------------|-------------|------|-----|-------|--------|------------------|-----|----------|-----|------|-----|

|        | nt00              | dma(        | sd0 | nt02 | ebc         | it0<br>nt03 | pll0 | gt  | rt0   |        | rt1              |     | rt2      |     | rt3  |     |

|        | nt08              | mt00        |     |      | mt04        | it1<br>nt16 | dt0  |     | et0   |        | et1              |     | et2      |     | e    | t3  |

|        | nt09              | mt01        |     |      | mt05        | it2<br>nt17 | dt1  |     | e     | t4 et5 |                  | et6 |          | e   | t7   |     |

| 18.3mm | nt10              | mt02        |     |      | mt06        | it3<br>nt18 | dt2  |     | е     | t8     | et9              |     | et10     |     | et11 |     |

|        | nt11              | mt03        |     |      | mt07        | it4<br>nt19 | dt3  |     | et    | :12    | et13             |     | et14     |     | et15 |     |

|        | nt15              | mt11        |     |      | mt15        | nt23<br>⊅ł! | ctb  |     | 21    | -tə    | £t19             |     | ₽L19     |     | 91   | .ţə |

|        | nt14              | mt10        |     |      | mt14        | nt22<br>Eł! | dt2  |     | 819 ( |        | 0 <sup>etə</sup> |     | 0119 111 |     | .19  |     |

|        | nt13              | mt09        |     | r    | nt13        | nt21<br>Zi! | ttb  |     | ₽ţ₽   |        | сtэ              |     | 9t9      |     | ∑t∋  |     |

|        | 80tm ut           |             |     | mt12 | nt20<br>L1! | 0tb         |      | 019 |       | ¢†9    |                  | Stə |          | 6t3 |      |     |

| ↓<br>↓ | nt04              | dma1<br>102 | sd1 | nt06 | c2c         | nt07<br>01! | pll1 | ţ6  | 40    |        | ţμ               |     | ЧS       |     | ւկց  |     |

|        | GP1               |             |     |      |             |             |      |     |       |        |                  |     |          |     |      |     |

#### **TRIPS Working Floorplan (to scale)**

# Prototype Simplifications

- Architecture simplifications

- No hardware cache coherence mechanisms

- No floating-point divider

- No native exception handling

- Simplified exception reporting

- Limited support for variable-sized blocks

- Microarchitecture simplifications

- No I-cache prefetching or block predict for I-cache refill

- No variable resource allocation (for smaller blocks)

- One cycle per hop on every network

- No clock-gating

- Direct-mapped and replicated LSQ (non-associative, oversized)

- No selective re-execution

- No fast block refetch

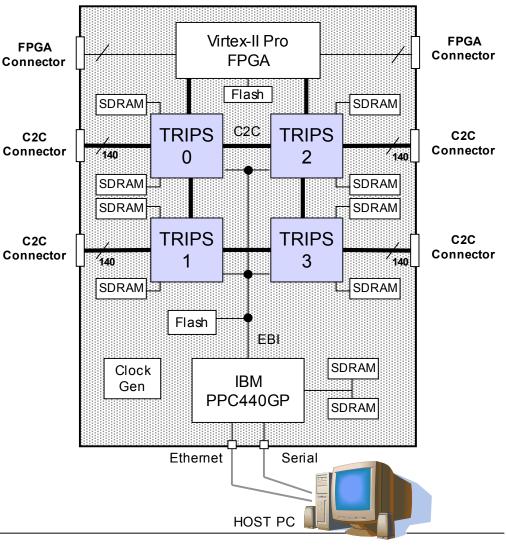

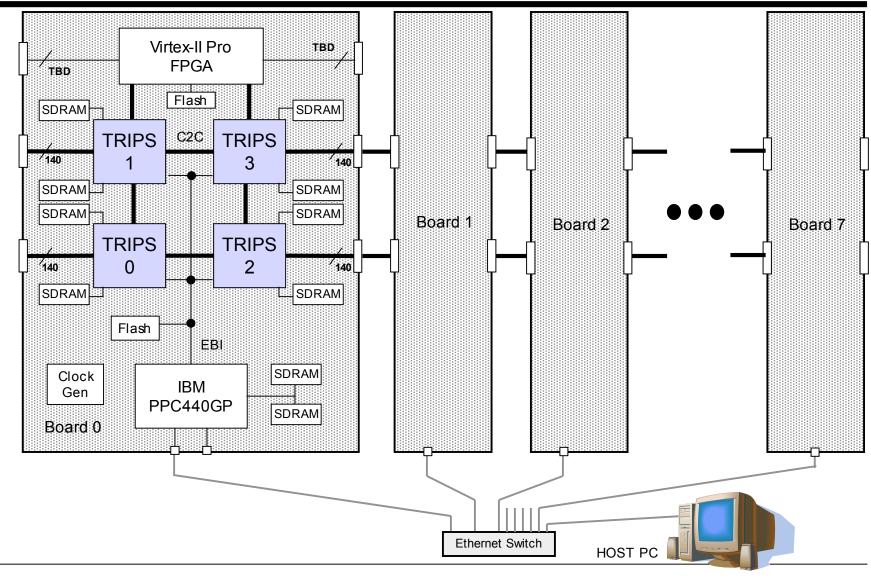

### TRIPS Prototype System Board

- TRIPS chip network

- 4 TRIPS chips (8 processors) per board

- Connected using a 2x2 chip-to-chip network

- Each chip provides local and remote access to 2GB SDRAM

- PPC440GP

- Configures and controls the TRIPS chips

- Connects to a Host PC for user interface (via serial port or ethernet)

- Runs an embedded Linux OS

- Includes a variety of integrated peripherals

- SDRAM DIMMs

- 8 slots for up to 8 GB TRIPS memory

- 2 slots for up to 1 GB PPC memory

- FPGA usage TBD but may include

- Protocol translator for high-speed I/O devices

- Programmable acceleration engine

**TRIPS BOARD**

### Maximum Size TRIPS System

### **TRIPS** Prototype System Capabilities

- Clock speeds

- 533MHz internal clock

- 266MHz C2C clock

- 133/266 SDRAM clock

- Single chip

- 2 processors per chip each with

- 64 KB L1-I\$, 32KB L1-D\$

- 8.5 Gops or GFlops/processor

- 17 Gops or Gflops/chip peak

- Up to 8 threads

- 1 MB on-chip memory

- L2 cache or scratchpad

- 2 GB SDRAM

- 2.2 GB/sec DRAM bandwidth

- Full system (8 boards)

- 32 chips, 64 processors

- 1024 64-bit FPUs

- 545 Gops/Gflops

- Up to 256 threads

- 64GB SDRAM

- 70 GB/s aggregate DRAM bandwidth

- 6.8 GB/sec C2C bisection bandwidth

### Code Examples

#### **ISCA-32** Tutorial

Robert McDonald

Department of Computer Sciences The University of Texas at Austin

#### Two Examples

- Vector Add Example

- A simple for loop

- Basic unrolling

- TRIPS Intermediate Language (TIL)

- Block Dataflow Graph

- Placed Instructions

- TRIPS Assembly Language (TASL)

- Sample Execution

- Linked List Example

- A while loop with pointers

- TRIPS predication

- Predicated loop unrolling

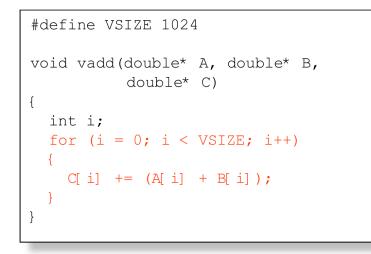

#### Vector Add – C Code

enter i = 0 C[i] += A[i] + B[i] i++ i < 1024 F T return

- Consider this simple C routine

- The routine does an add and accumulate for fixed-size vectors

- An initial control flow graph is shown

#### Vector Add – Unrolled

- This loop wants to be unrolled

- Unrolling reduces the overhead per loop iteration

- It reduces the number of conditional branches that must be executed

#### Vector Add – TIL Code

| .bbegin | vadd\$1                      |

|---------|------------------------------|

| read    | \$t0, \$g70                  |

| read    | \$t1, \$g71                  |

| read    | \$t2, \$g72                  |

| read    | \$t3, \$g73                  |

| ld      | \$t4, (\$t1) L[0]            |

| ld      | \$t5, (\$t2) L[1]            |

| ld      | \$t6, (\$t3) L[2]            |

| fadd    | \$t7, \$t5, \$t6             |

| fadd    | \$t8, \$t4, \$t7             |

| sd      | (\$t1), \$t8 S[3]            |

| ld      | \$t9, 8(\$t1) <u>L[</u> 4]   |

| ld      | \$t10, 8(\$t2) L[5]          |

| ld      | \$t11, 8(\$t3) L[6]          |

| fadd    | \$t12, \$t10, \$t11          |

| fadd    | \$t13, \$t9, \$t12           |

| sd      | 8(\$t1), \$t13 S[7]          |

| ld      | \$t14, 16(\$t1) ∐ 8]         |

| ld      |                              |

|         | \$t16, 16(\$t3) Ц[10]        |

|         | \$t17, \$t15, \$t16          |

|         | \$t18, \$t14, \$t17          |

| sd      | 16(\$t1), \$t18 S[11]        |

| ld      | \$t19, 24(\$t1) <u>[</u> 12] |

| ld      | \$t20, 24(\$t2) <u>[</u> 13] |

| ld      | \$t21, 24(\$t3) [[14]        |

|         | \$t22, \$t20, \$t21          |

| fadd    | \$t23, \$t19, \$t22          |

| sd      | 24(\$t1), \$t23 S[15]        |

| ld      | \$t24, 32(\$t1) <u>[</u> 16] |

| ld      | \$t25, 32(\$t2) [[17]        |

| ld      | \$t26, 32(\$t3) L[18]        |

|         | \$t27, \$t25, \$t26          |

| fadd    | \$t28, \$t24, \$t27          |

| sd      | 32(\$t1), \$t28 S[19]        |

| (conti  | inued)                       |

|         |                              |

ld \$t29, 40(\$t1) I[ 20] ld \$t30, 40(\$t2) L[21] ld \$t31, 40(\$t3) L[22] fadd \$t32, \$t30, \$t31 fadd \$t33, \$t29, \$t32 sd 40(\$t1), \$t33 S[23] ld \$t34, 48(\$t1) <u>[</u>24] ld \$t35, 48(\$t2) I[25] ld \$t36, 48(\$t3) L[26] fadd \$t37, \$t35, \$t36 fadd \$t38, \$t34, \$t37 sd 48(\$t1), \$t38 S[27] ld \$t39, 56(\$t1) 4[28] ld \$t40, 56(\$t2) L[29] ld \$t41, 56(\$t3) [[ 30] fadd \$t42, \$t40, \$t41 fadd \$t43, \$t39, \$t42 56(\$t1), \$t43 S[31] sd addi \$t45, \$t0, 8 addi \$t47, \$t1, 64 addi \$t49, \$t2, 64 addi \$t51, \$t3, 64 genu \$t52, 1024 \$t54, \$t45, \$t52 tlt bro t<\$t54> vadd\$1 bro f<\$t54> vadd\$2 write \$q70, \$t45 write \$g71, \$t47 write \$q72, \$t49 write \$q73, \$t51 .bend

- The compiler produces TRIPS Intermediate Language (TIL) files

- Each file defines one or more program blocks

- Each block includes instructions, normally listed in program order

- Instructions are defined using a familiar syntax (name, target, sources)

- Read and write instructions access registers

- All other instructions deal with temporaries

- Notice the Load/Store IDs

- Notice the predicated branches

June 4, 2005

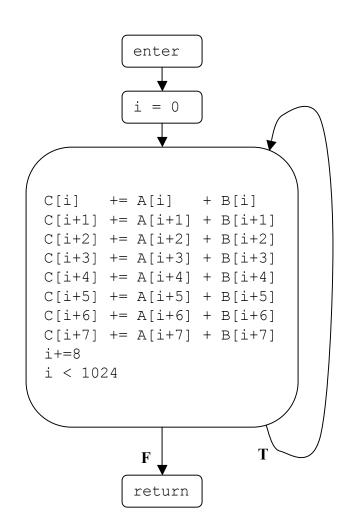

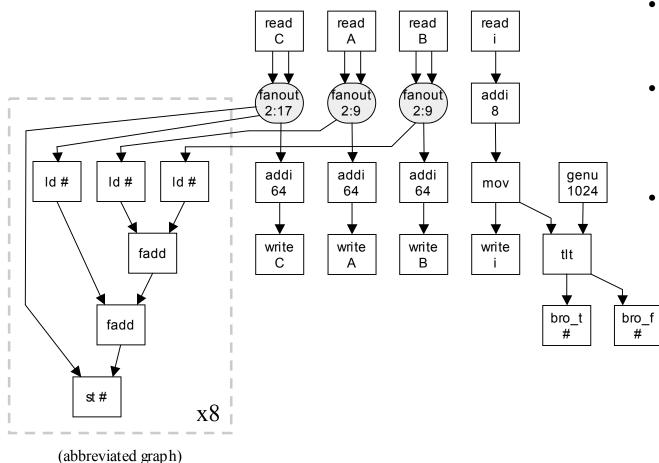

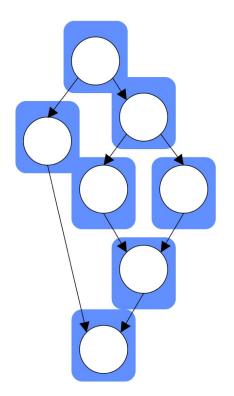

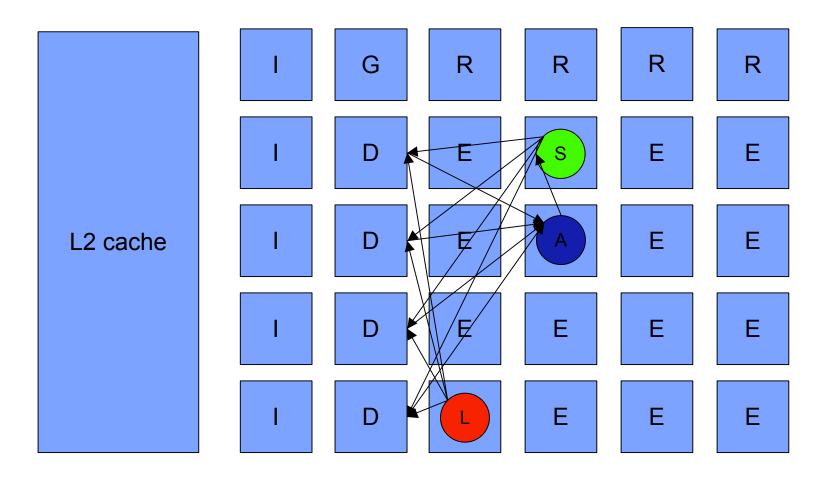

#### Vector Add – Block Dataflow Graph

- Read and load instructions gather block inputs

- Write, store, and branch instructions produce block outputs

- Address fanout can present an interesting challenge

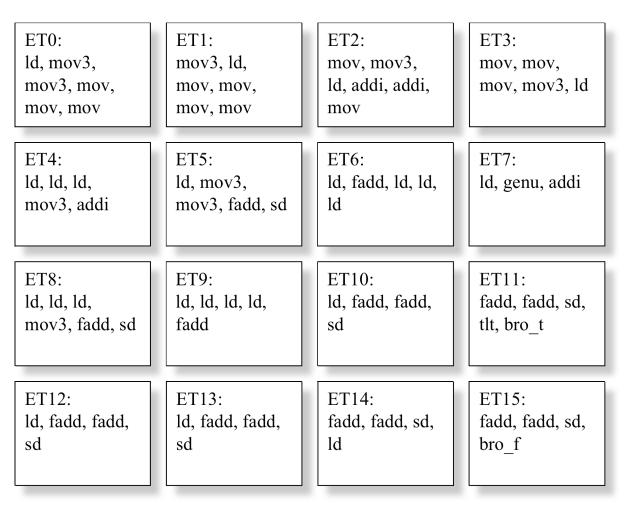

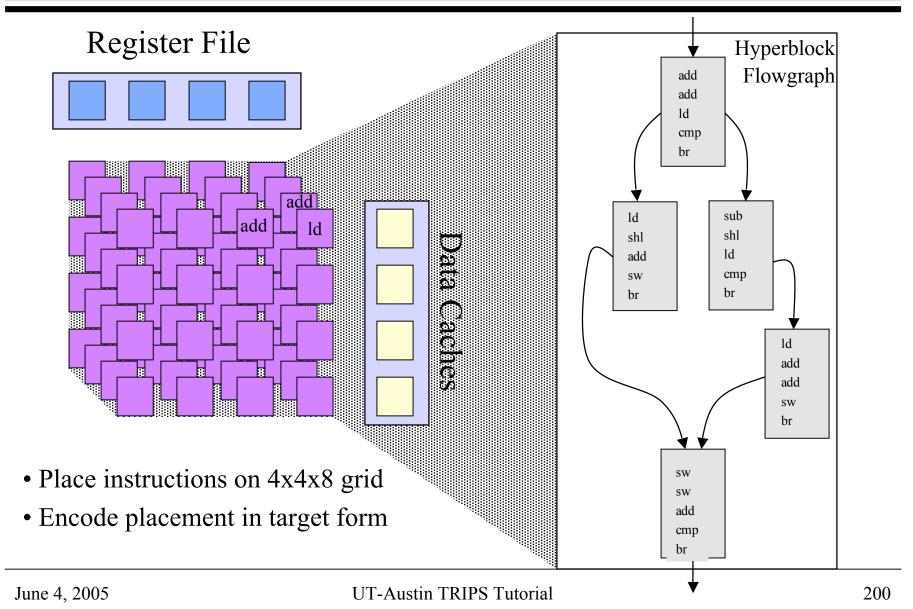

#### Vector Add – Placed Instructions

- The scheduler analyzes each block dataflow graph

- It inserts fanout instructions, as needed

- It places the instructions within the block (they don't have to be in program order)

- It produces assembly language files

- An instruction fires when its operands become available (regardless of position)

#### Vector Add – TASL Code

| -      |                                  |

|--------|----------------------------------|

| .bbegi | n vadd\$1                        |

| R[ 2]  | read G[70] N[14,0]               |

| R[ 3]  | read G[71] N[43,0] N[3,0]        |

| R[ 0]  | read G[72] N[48,0] N[12,0]       |

| R[ 1]  | read G[73] N[18,0] N[13,0]       |

|        |                                  |

| N[3]   | mov N[7,0] N[9,0]                |

| N[7]   | mov N[11,0] N[2,0]               |

| N[9]   | mov N[4,0] N[37,0]               |

| N[ 11] | mov N[15,0] N[6,0]               |

| N[2]   | mov N[1,0] N[75,0]               |

| N[ 4]  | mov3 N[32,0] N[78,0] N[64,0]     |

| N[37]  | mov3 N[49,0] N[65,0] N[84,0]     |

| N[ 15] | mov3 N[19,0] N[109,0] N[10,0]    |

| N[6]   | mov3 N[108,0] N[5,0] N[106,0]    |

| N[ 1]  | mov3 N[0,0] N[107,0] N[33,0]     |

| N[ 12] | mov N[16,0] N[76,0]              |

| N[16]  | mov N[44,0] N[21,0]              |

| N[76]  | mov3 N[ 66,0] N[ 77,0] N[ 110,0] |

| N[44]  | mov3 N[72,0] N[96,0] N[73,0]     |

| N[21]  | mov N[35,0] N[42,0]              |

| N[13]  | mov N[17,0] N[41,0]              |

| N[17]  | mov N[8,0] N[20,0]               |

| N[ 41] | mov3 N[69,0] N[97,0] N[34,0]     |

| N[8]   | mov3 N[36,0] N[68,0] N[40,0]     |

| N[20]  | mov N[46,0] N[50,0]              |

| N[ 32] | ld L[0] N[74,0]                  |

| N[66]  | ld [1] N[70,0]                   |

| N[69]  | ld [2] N[70,1]                   |

| N[70]  | fadd N[74,1]                     |

| N[74]  | fadd N[ 78,1]                    |

| N[78]  |                                  |

| N[64]  |                                  |

| N[77]  | ld L[5] 8 N[38,0]                |

| (cont) |                                  |

|        |                                  |

N 97] ld L[6] 8 N[38,1] N 381 fadd N[ 45,1] fadd N[ 49,1] N[45] N[49] sd S[7] 8 N[65] ld L[8] 16 N[80,0] N[110] ld L[9] 16 N[81,0] N[34] ld L[10] 16 N[81,1] N[81] fadd N[80,1] N[80] fadd N[ 84,1] N[84] sd S[11] 16 N[19] ld L[12] 24 N[105,0] N[72] ld L[13] 24 N[101,0] N[36] ld L[14] 24 N[101,1] N[101] fadd N[105,1] N[105] fadd N[109,1] N[109] sd S[15] 24 N[10] ld L[16] 32 N[104,0] N[96] ld L[17] 32 N[100,0] N[68] ld L[18] 32 N[100,1] N[100] fadd N[104,1] N[104] fadd N[108,1] N[108] sd S[19] 32 ld L[20] 40 N[102,0] N[5] N[73] ld L[21] 40 N[98,0] N[40] ld L[22] 40 N[98,1] N[98] fadd N[102,1] N[102] fadd N[106,1] N[106] sd S[23] 40 ld L[24] 48 N[103,0] N[0] N[35] ld L[25] 48 N[99,0] N[46] ld L[26] 48 N[99,1] N[99] fadd N[103,1] N[103] fadd N[107,1] N[107] sd S[27] 48 (cont)

N 331 ld [28] 56 N[71,0] ld L[29] 56 N[67,0] N 42] N[50] ld L[30] 56 N[67,1] N[ 67] fadd N[ 71,1] N[71] fadd N[75,1] N[75] sd S[31] 56 N[14] addi 8 N[22,0] N[22] mov N[79,0] W[2] N[ 43] addi 64 W[3] N[ 48] addi 64 W[0] N[18] addi 64 W[1] N[39] genu 1017 N[79,1] N[79] tlt N[83,p] N[111,p] N[83] bro t vadd\$1 N[111] bro f vadd\$2 write G[70] W[2] W[3] write G[71] W[0] write G[72] W[1] write G[73] .bend

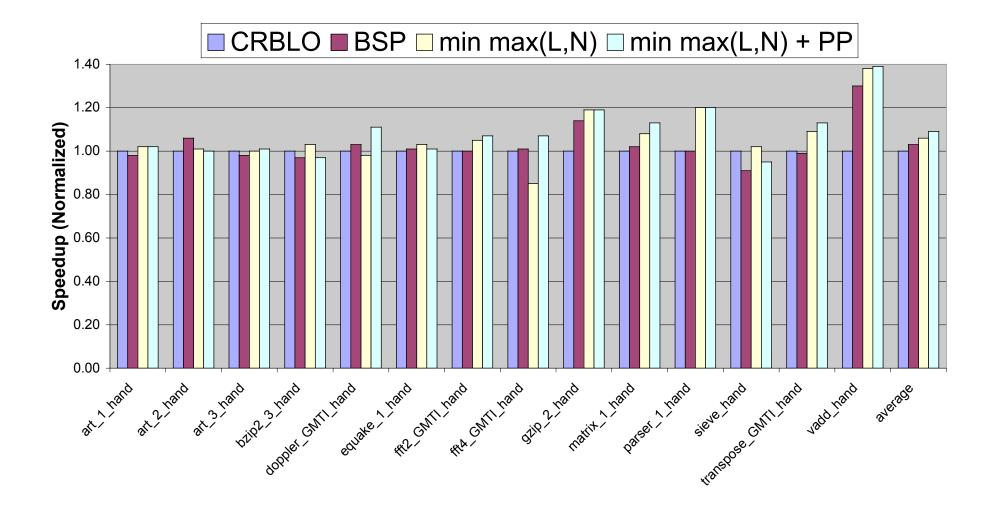

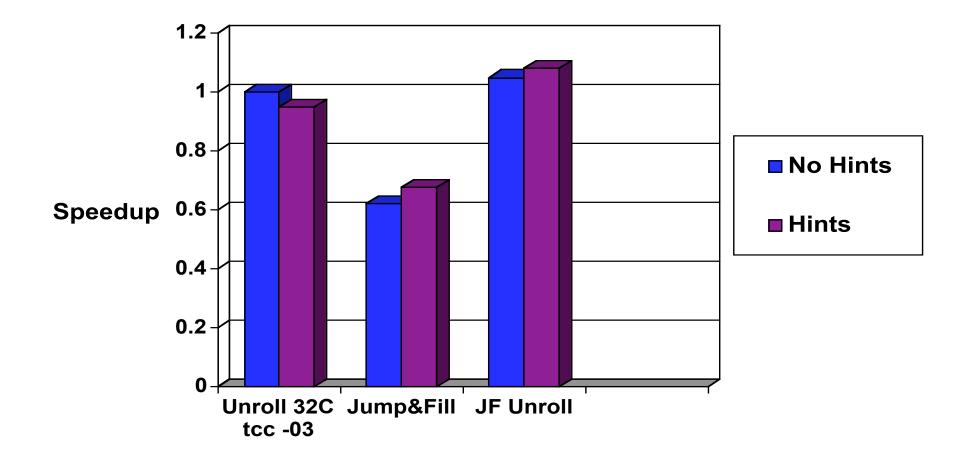

- TRIPS Assembly Language (TASL) files are fed to the assembler

- Instructions are described using a dataflow notation

- The TRIPS processor can execute up to 8 blocks concurrently

- This diagram shows block latency and throughput for an optimal vector add loop

- It achieves ~7.4 IPC, ~3.2 loads & stores per cycle

#### Linked List – C Code

```

// type info

struct foo

long tag;

long value;

struct foo * next;

};

struct foo * head;

void list add( long key )

struct foo * p = head;

// search list and increment node

while (p)

if (p \rightarrow tag == key)

p->value++;

break;

p = p - > next;

// ...

```

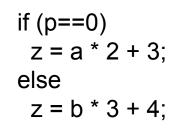

- For a second example, let's examine something more complex

- We'll be focusing upon the code in red

- A linked list operation is performed using a while loop and search pointer

- The number of while loop iterations can vary

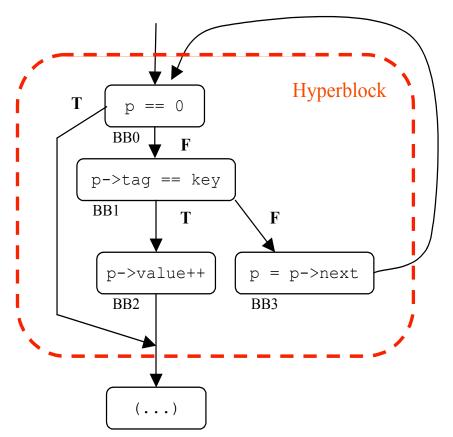

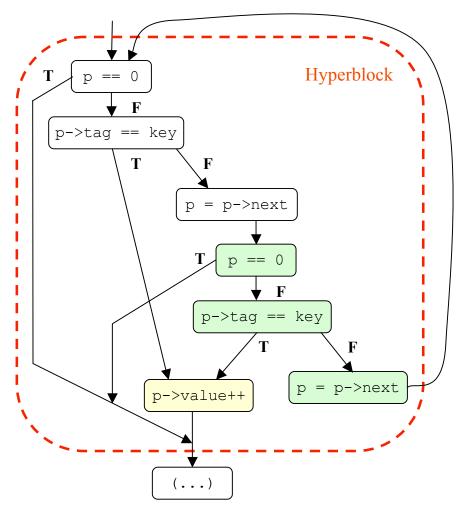

#### Linked List – CFG

- The while loop's control flow graph is shown here

- It consists of four rather small basic blocks

- Its hard to get anywhere fast with all of those branches

- We'd like to use predication to form a larger program block (or *hyperblock*)

### Linked List – Hyperblock #1

```

.bbegin block1

read $t0, $g70

; key

read $t1, $q71

; p

; BB0

teqi $p0, $t1, 0

; BB1

ld $t3, ($t1)

; p->taq

teq f <$p0> $p1, $t3, $t0

ld $t4, 16($t1) ; p->next

; BB2

ld $t10, 8($t1) ; p->data

null t <$p0> $t11

addi t <$p1> $t11, $t10, 1

null f <$p1> $t11

sd 8($t1), $t11

; p->data

; BB3

null t <$p0,$p1> $t99

mov f <$p1> $t99, $t4

write $q71, $t99

; p

; branches

bro t <$p0, $p1> block2

bro f <$p1> block1

.bend

```

- Here is a TIL representation of the hyperblock

- Predicate p0 represents the test to determine whether p is null

- Predicate p1 represents the test to determine whether the tag matches the key

- The test instruction that produces p1 is itself predicated upon p0 being false

- That means that there are only three possible predicate outcomes:

- p0 true, p1 unresolved

- p0 false, p1 false

- p0 false, p1 true

- This example demonstrates "predicate-oring", which allows multiple exclusive predicates to be OR'd at the target instruction

- This example demonstrates write and store nullification, which allows block outputs to be cancelled

- Loads are allowed to execute speculatively because exceptions will be predicated downstream

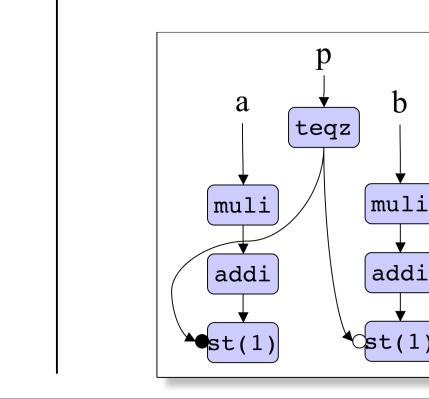

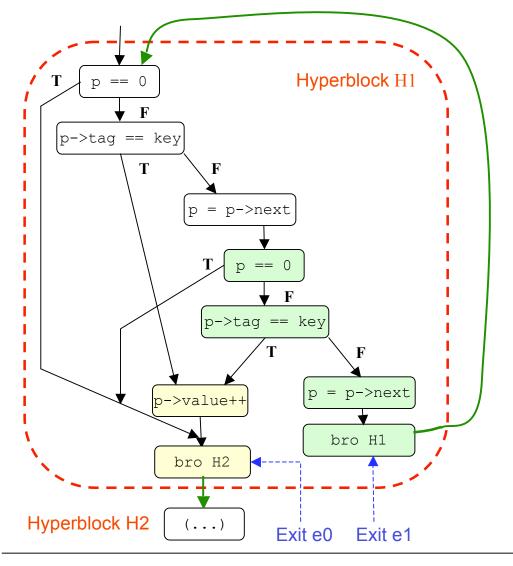

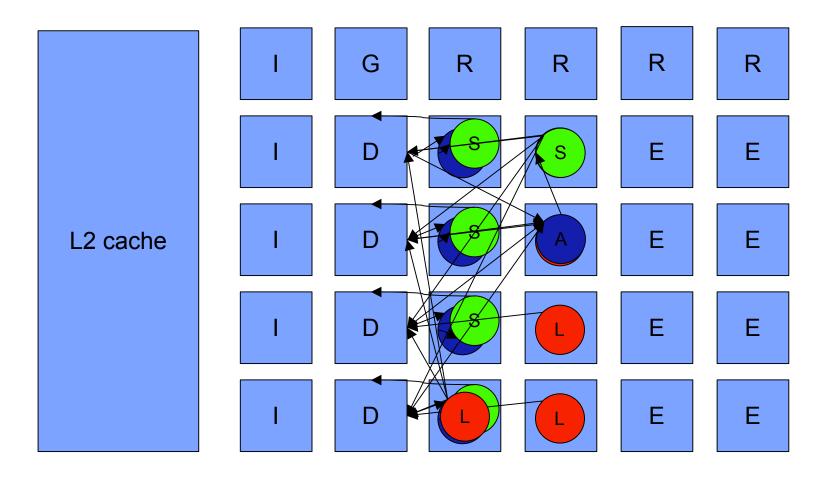

#### Linked List – Predicated Loop Unrolling

- With predication, it's also possible (and helpful) to unroll this loop

- Many variations are possible

- This diagram shows just two iterations within the hyperblock

- There number of block exits and block outputs remains the same as before

- The compiler can use static heuristics or profile data to choose an unrolling factor

- Can sometimes use instruction merging to combine multiple statements into one (in yellow)

### Linked List – Hyperblock #2

```

.bbegin block1

read $t0, $q70

; key

read $t1, $g71

; p

teqi $p0, $t1, 0

ld $t3, ($t1)

; p->tag

teq f <$p0> $p1, $t3, $t0

ld $t4, 16($t1)

; p->next

teqi f <$p1> $p2, $t4, 0

ld $t5, ($t4) ; p->next->tag

teq f <$p2> $p3, $t5, $t0

ld $t6, 16($t4)

; p->next->next

; conditional p update

null t <$p0,$p1> $t99

mov t <$p2,$p3> $t99, $t4

mov f <$p3> $t99, $t6

write $g71, $t99

; p

; conditional p->data update

ld t <$p1> $t10, 8($t1)

ld f <$p1> $t10, 8($t4)

null t <$p0, $p2> $t11

addi t <$p1, $p3> $t11, $t10, 1

null f <$p3> $t11

sd 8($t1), $t11

; p->data

; branches

bro t <$p0, $p1, $p2, $p3> block2

bro f <$p3> block1

.bend

```

- Here is some TIL for the unrolled while loop

- The changes from the first version are highlighted (in red)

- Notice the use of predicate-ORing, which allows the block to finish executing early in some cases

- There are now four predicates and five possible outcomes

| p0 | p1 | p2 | p3 |  |  |

|----|----|----|----|--|--|

| Т  | -  | -  | -  |  |  |

| F  | Т  | -  | -  |  |  |

| F  | F  | Т  | -  |  |  |

| F  | F  | F  | Т  |  |  |

| F  | F  | F  | F  |  |  |

### Conclusion

- The EDGE ISA allows instructions to be both *fetched* and *executed* out-of-order with minimal book-keeping

- It's possible to use loop unrolling and predication to form large blocks

- The TRIPS predication model allows control flow to be converted into an efficient dataflow representation

- Operand fanout is more explicit in an EDGE ISA and costs extra instructions

### Global Control

#### **ISCA-32** Tutorial

Ramadass Nagarajan

Department of Computer Sciences The University of Texas at Austin

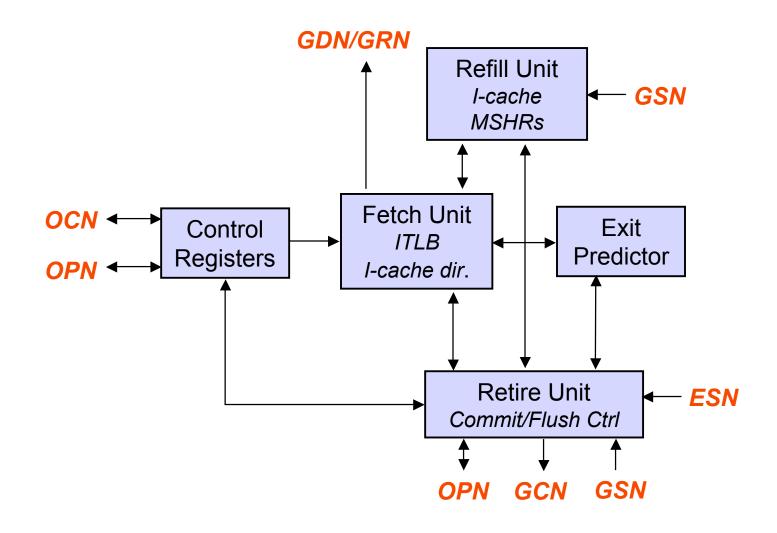

#### G-Tile Location and Connections

## Major G-Tile Responsibilities

- Orchestrates global control for the core

- Maps blocks to execution resources

- Instruction fetch control

- Determines I-cache hits/misses, ITLB hits/misses

- Initiates I-cache refills

- Initiates block fetches

- Next-block prediction

- Generates speculative block addresses

- Block completion detection and commit initiation

- Flush detection and initiation

- Branch mispredictions, Ld/St dependence violations, exceptions

- Exception reporting

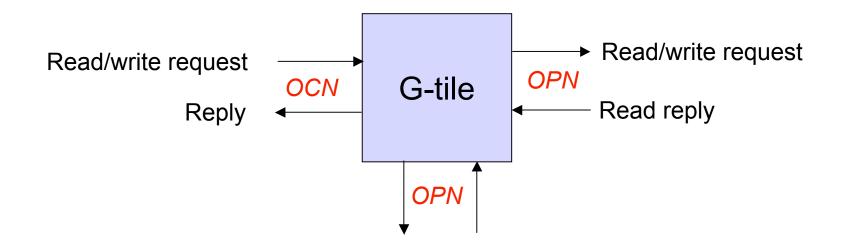

## Networks Used by G-Tile

- **OPN** Operand Network

- Receive and send branch addresses from/to E-tiles

- OCN On-Chip Network

- Receive block header from adjacent I-tile

- **GDN** Global Dispatch Network

- Send inst. fetch commands to I-tiles and read/write instructions to R-tiles

- GCN Global Control Network

- Send commit and flush commands to D-tiles, R-tiles and E-tiles

- **GRN** Global Refill Network

- Send I-cache refill commands to I-tile slave cache banks

- **GSN** Global Status Network

- Receive refill, store, and register write completion status and commit acknowledgements from I-tiles, D-tiles, and R-tiles

- ESN External Store Network

- Receive external store pending and error status from D-tiles

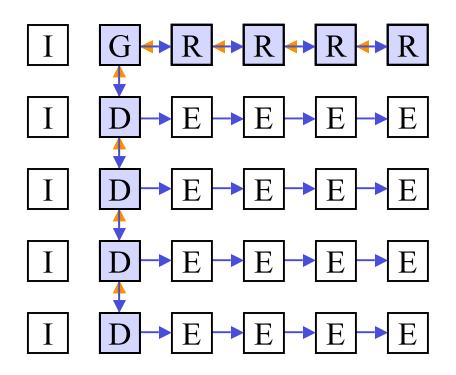

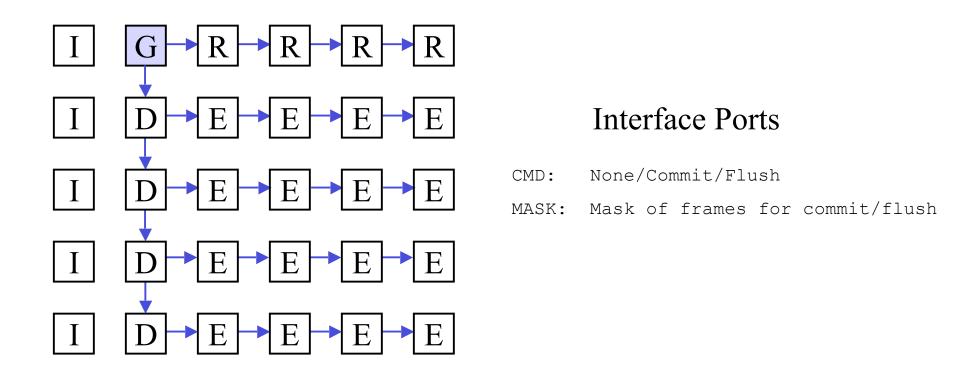

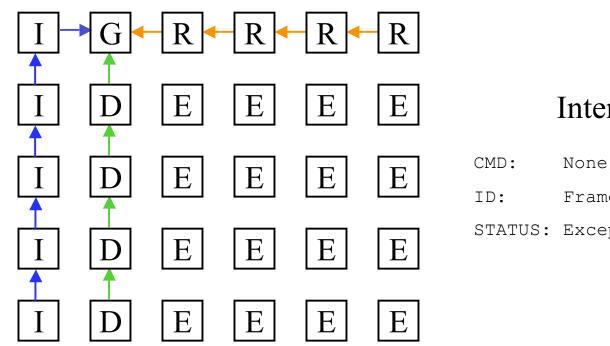

### Global Dispatch Network (GDN)

#### Interface Ports

- CMD: None/Fetch/Dispatch

- ADDR: Address of block

- SMASK: Store mask in block

- FLAGS: Block execution flags

- ID: Frame identifier

- INST: Instruction bits

- Delivers instruction fetch commands to I-tiles

- Dispatches instructions from I-Tiles to R-Tiles/E-Tiles

### Global Refill Network (GRN)

#### Interface Ports

- CMD: None/Refill

- RID: Refill buffer identifier

ADDR: Address of block to refill

Delivers refill commands to I-Tiles

### Global Control Network (GCN)

Delivers commit and flush commands to R-Tiles, D-Tiles and E-Tiles

### Global Status Network (GSN)

#### **Interface** Ports

- None/Completed/Committed

- Frame/Refill buffer identifier

STATUS: Exception Status

I-tiles: Completion status for pending refills

R-tiles: Completion status register writes, acknowledgement of register commits

D-tiles: Completion status for stores, acknowledgement of store commits

### External Store Network (ESN)

#### **Interface Ports**

PENDING: Pending status of external store requests and spills in each thread

ERROR: Errors encountered for external store requests and spills in each thread

Delivers external store pending and error status from D-tiles

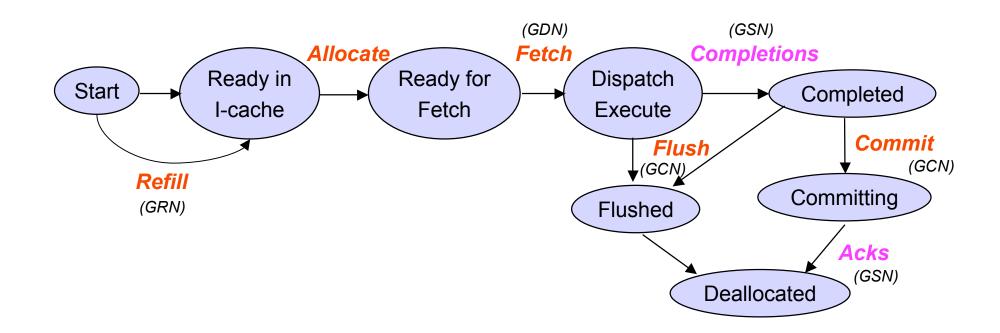

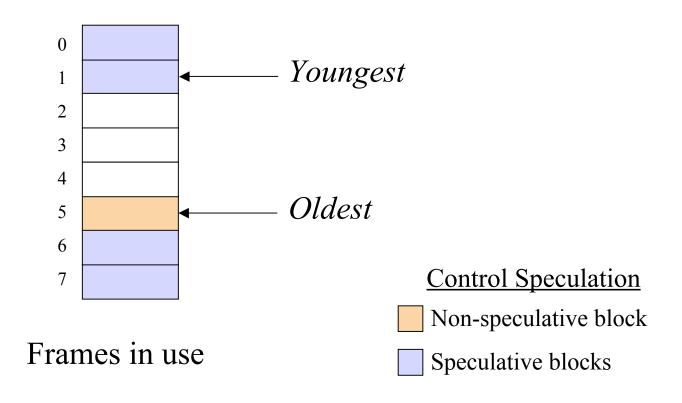

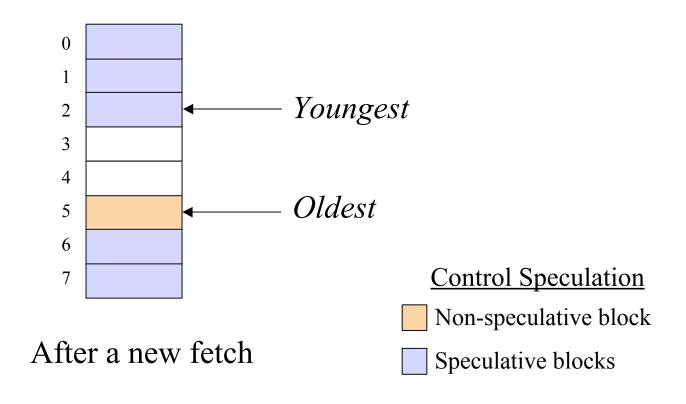

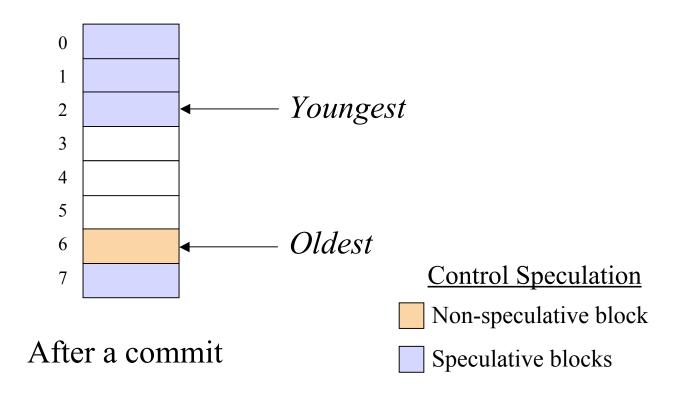

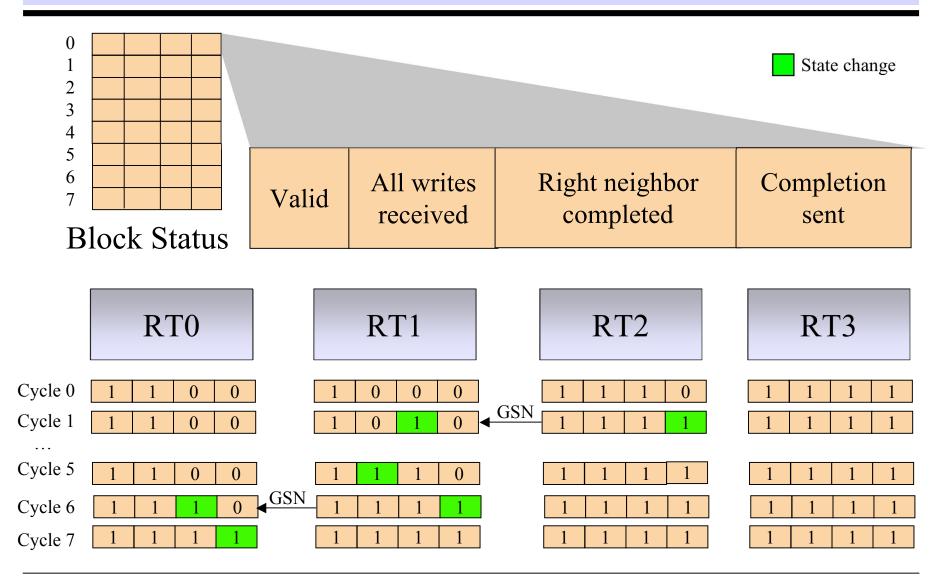

## Overview of Block Execution

#### Different states in the execution of a block

## Major G-Tile Structures

Frame Management

Frames allocated from a circular queue

### Frame Management

Frames allocated from a circular queue

Frame Management

Frames allocated from a circular queue

## Fetch Unit

- Instruction TLB

- 16 entries

- 64KB 1TB supported page size

- I-cache directory

- 128 entries

- Each entry corresponds to one cached block

- Entry Fields

- Physical tag for the block

- Store mask for the block

- Execution flags for the block

- 2-way set associative

- LRU replacement

- Virtually indexed, physically tagged

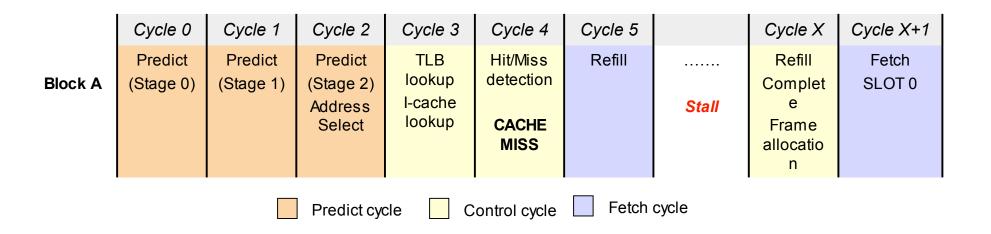

# Fetch Pipeline

|         | Cycle 0              | Cycle 1              | Cycle 2                                   | Cycle 3                            | Cycle 4                                      | Cycle 5              | Cycle 6              | Cycle 7              | Cycle 8         |

|---------|----------------------|----------------------|-------------------------------------------|------------------------------------|----------------------------------------------|----------------------|----------------------|----------------------|-----------------|

| Block A | Predict<br>(Stage 0) | Predict<br>(Stage 1) | Predict<br>(Stage 2)<br>Address<br>Select | TLB<br>Iookup<br>I-cache<br>Iookup | Hit/Miss<br>detection<br>Frame<br>allocation | Fetch<br>SLOT 0      | Fetch<br>SLOT 1      | Fetch<br>SLOT 2      | Fetch<br>SLOT 3 |

| Block B |                      |                      |                                           |                                    |                                              | Predict<br>(Stage 0) | Predict<br>(Stage 1) | Predict<br>(Stage 2) | Stall           |

|   | Cycle 9                                 | Cycle 10          | Cycle 11                           | Cycle 12                                     | Cycle           | Cycle 14        | Cycle 15        | Cycle 16        | Cycle 17        |

|---|-----------------------------------------|-------------------|------------------------------------|----------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|   | Fetch<br>SLOT 4                         | Fetch<br>SLOT 5   | Fetch<br>SLOT 6                    | Fetch<br>SLOT 7                              | 13              |                 |                 |                 |                 |

|   | Stall                                   | Address<br>Select | TLB<br>lookup<br>l-cache<br>lookup | Hit/Miss<br>detection<br>Frame<br>allocation | Fetch<br>SLOT 0 | Fetch<br>SLOT 1 | Fetch<br>SLOT 2 | Fetch<br>SLOT 3 | Fetch<br>SLOT 4 |

| • | Predict cycle Control cycle Fetch cycle |                   |                                    |                                              |                 |                 |                 |                 |                 |

# Refill Pipeline

- Refills stall fetches for the same thread

- Support for up to four outstanding refills one per thread

## Per-Frame State

#### Frame status

| V | Valid    |

|---|----------|

| 0 | Oldest   |

| Y | Youngest |

#### Block execution status

| RC | Registers completed     |  |  |  |  |

|----|-------------------------|--|--|--|--|

| SC | Stores completed        |  |  |  |  |

| BC | Branch completed        |  |  |  |  |

| Е  | Exception reported      |  |  |  |  |

| L  | Load violation reported |  |  |  |  |

#### Block commit status

| CS  | Commit sent         |

|-----|---------------------|

| RCT | Registers committed |

| SCT | Stores committed    |

#### Branch prediction status

| BADDR  | Block address                                    |

|--------|--------------------------------------------------|

| NADDR  | Next block address                               |

| NSTATE | Next block address state (predicted or resolved) |

| М      | Branch misprediction detected                    |

| РС     | Prediction completed                             |

| RC     | Repair completed                                 |

| UC     | Update completed                                 |

| Commit  | ← | V | & O & RC & SC & BC |

|---------|---|---|--------------------|

|         |   | & | ~E & ~L & ~CS      |

|         |   |   |                    |

| Dealloc | ← | v | & O & CS           |

|         |   | & | RCT & SCT & UC     |

|         |   |   |                    |

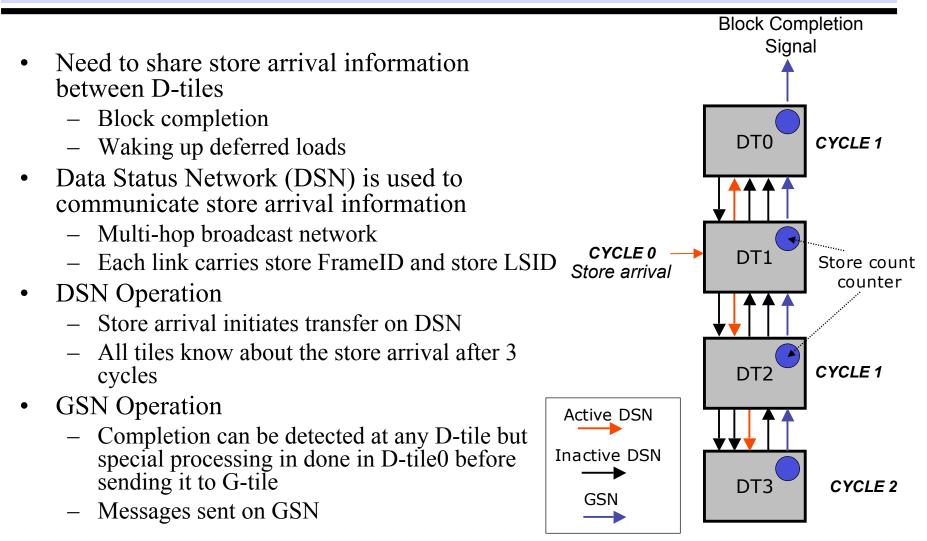

## **Block Completion Detection**

- Block completed execution if:

- All register writes received

- All stores received

- Branch target received

- Register completion tracked locally at each R-Tile

- Expected writes at each R-Tile known statically

- Completion status forwarded from farthest R-Tile to the G-Tile on the GSN

- Store completion reported by D-tile 0

- All D-Tiles communicate with each other to determine completion

- Completion status delivered on the GSN by D-tile 0

# **Commit Pipeline**

| Cycle 0                             | Cycle 1       | Cycle 2              | Cycle X                        | Cycle X+1             |

|-------------------------------------|---------------|----------------------|--------------------------------|-----------------------|

| Register/Branch/<br>Store           | Commit detect | Commit send<br>(GCN) | <br>Commit acks received (GSN) | Frame<br>deallocation |

| Completion<br>received<br>(GSN/OPN) |               | Predictor<br>Commit  |                                |                       |

- Block ready for commit if:

- Oldest in the thread

- Completed with no exceptions

- No load/store dependence violations detected

- Commit operation

- G-Tile sends commit message for a block on the GCN

- R-Tiles and D-Tiles perform local commit operations

- R-Tiles and D-Tiles acknowledge commit using GSN

- G-Tile updates predictor history for the block

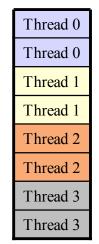

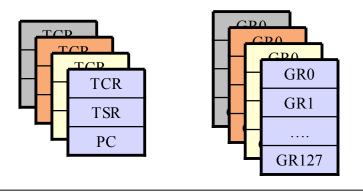

# **T-Morph Support**

- Up to four threads supported in T-morph mode

- Threads mapped to fixed set of frames

- Per-thread architected registers in the G-tile

- Thread Control and Status Registers

- Program Counter (PC)

- Other T-morph support state/logic

- Per-thread frame management

- Round-robin thread prioritization for block fetch/commit/flush

#### Frame Allocation

## **Exception Reporting**

- Exceptions reported to the G-tile

- GSN: refill exceptions, execute exceptions delivered to stores, register outputs

- OPN: execute exceptions delivered to branch targets

- ESN: errors in external stores

- G-tile halts processor whenever exception occurs

- Speculative blocks in all threads flushed

- Oldest blocks in all threads completed and committed

- All outstanding refills, stores and spills completed

- Signals EBC to cause external interrupt

- Exception type reported in PSR and TSRs

- Multiple exceptions may be reported

#### Exceptions detected at G-tile

| Breakpoint  |  |  |  |  |  |

|-------------|--|--|--|--|--|

| Timeout     |  |  |  |  |  |

| System Call |  |  |  |  |  |

| Reset       |  |  |  |  |  |

| Fetch       |  |  |  |  |  |

| Interrupt   |  |  |  |  |  |

#### Exceptions detected at other tiles

## **Control Flow Prediction**

#### **ISCA-32** Tutorial

Nitya Ranganathan

Department of Computer Sciences The University of Texas at Austin

## Predictor Responsibilities

- Predict next block address for fetch

- Predict block exit and exit branch type (branches not seen by predictor)

- Predict target of exit based on predicted branch type

- Predictions amortized over each large block

- Maximum necessary prediction rate is one every 8 cycles

- Speculative update for most-recent histories

- Keep safe copies around to recover from mispredictions

- Repair predictor state upon a misprediction

- Update the predictor upon block commit

- Update exits, targets and branch types with retired block state

### Example Hyperblock from Linked List Code

- Each hyperblock may have several predicated exit branches

- Exit e0 → block H2

- Exit e1  $\rightarrow$  block H1

- Only one branch will fire

- Predictor uses exit IDs to make prediction

- 8 exit IDs supported

- e0 → "000"

- e1 **→** "001"

- Predictor predicts the ID of the exit that will fire

- implicitly predict several predicates in a path

- Exit history formed by concatenating sequence of exit IDs

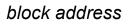

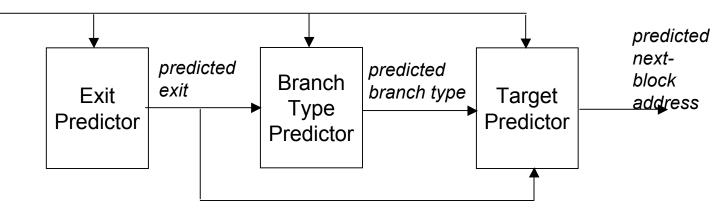

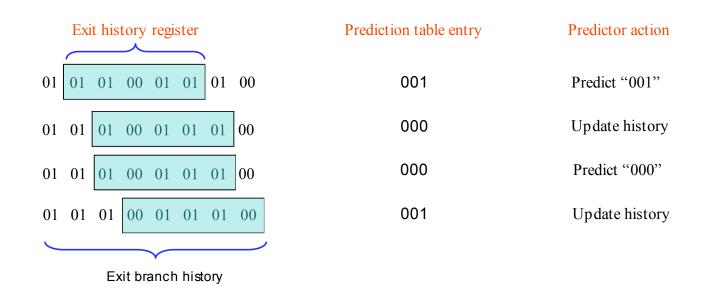

## High-level Predictor Design

- Index exit predictor with current block address

- Use exit history to predict 1 of 8 exits

- Predict branch type (call/return/branch) for chosen exit

- Index multiple target predictors with block address and predicted exit

- Choose target address based on branch type

## Predictor Components

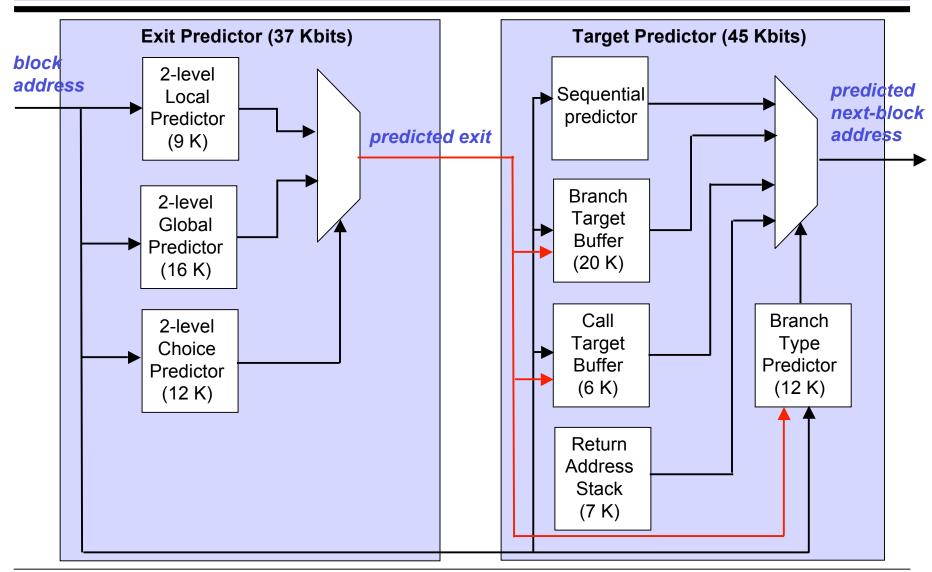

## Prediction using Exit History (linked list example)

- Dynamic block sequence H1 H1 H1 H2 H1 H1

- Local exit history for block H1

- H1 H2 e1 e0 e1 el e0 el el el 00 01 01 00 01 01 01 01

- Use only 2 bits from each 3-bit exit to permit longer histories

- History table entry holds 5 exit IDs

Local exit history encoding (2 bits)

• Prediction table contains exit IDs and hysteresis bits

۲

June 4, 2005

## More Predictor Features

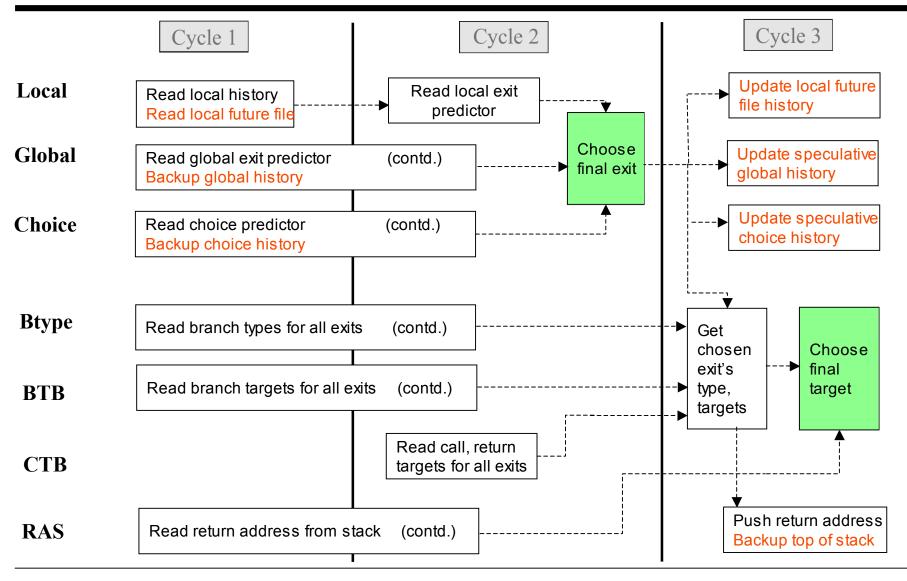

- Speculative state buffering

- Latest global histories in global and choice history registers

- Old snapshots of histories stored in history file for repair

- Latest local history maintained in future file

- Local exit history table holds committed block history

- Return address stack state buffering

- Save top of stack pointer and value before every prediction

- Repair stack on address and branch type mispredictions

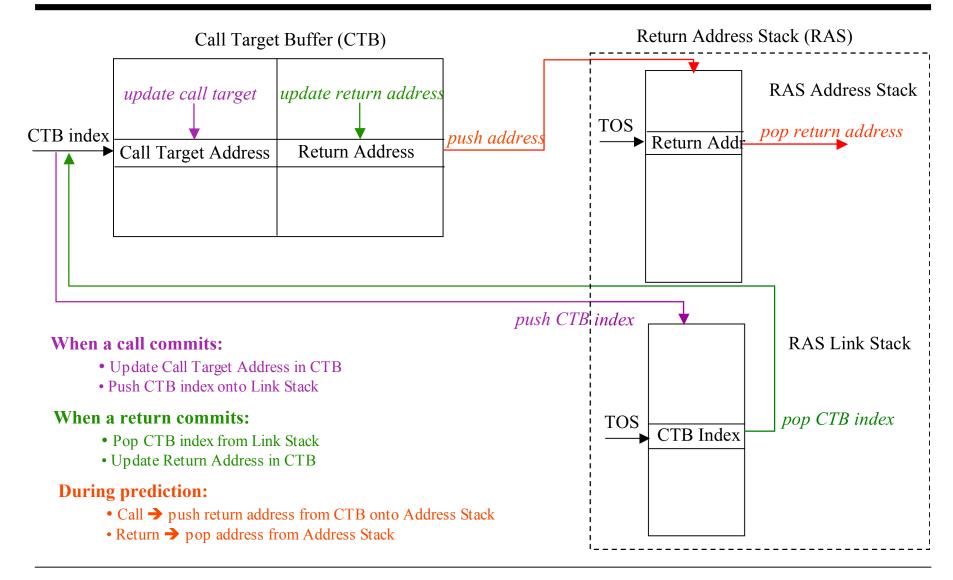

- Call-return

- Call/return instructions enforce proper control flow

- Predictor learns to predict return addresses using call-return link stack

- Update stores return address in link stack corresponding to call stored in CTB

### Learning Call-Return Relationships

UT-Austin TRIPS Tutorial

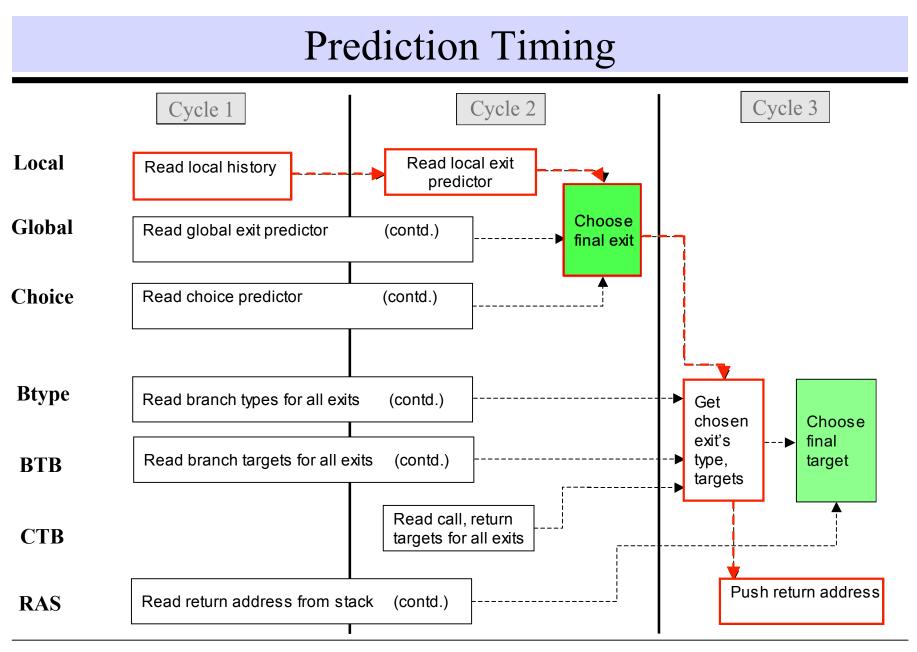

## Prediction and Speculative Update Timing

June 4, 2005

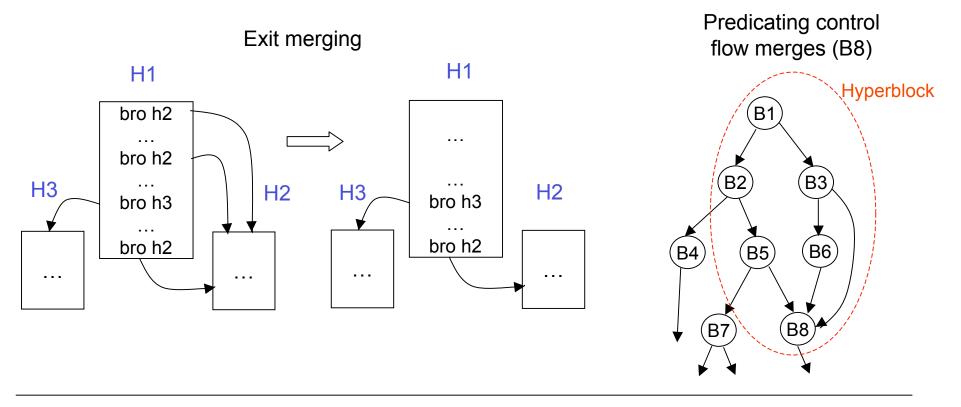

## Optimizations for Better Prediction

- Exit prediction more difficult than branch prediction

- 1 of 8 vs. 1 of 2

- Fewer exits in block  $\rightarrow$  better predictability

## Instruction Fetch

#### **ISCA-32** Tutorial

Haiming Liu

Department of Computer Sciences The University of Texas at Austin

## I-Tile Location and Connections

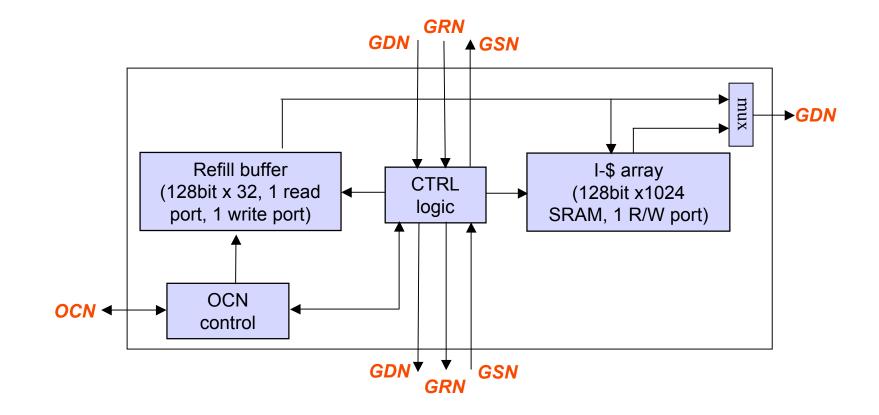

# I-Tile Major Responsibilities

- Instruction Fetch

- Cache instructions for one row of R-Tiles/E-Tiles

- Dispatch instructions to R-Tiles/E-Tiles through GDN

- Instruction Refill

- Receive refill commands from G-Tile on GRN

- Submit memory read requests to the N-Tile on OCN

- Keep track of completion status of each ongoing refill

- Report completion status to G-Tile on the GSN when refill completes

- OCN Access Control

- Share N-Tile connection between I-Tile and D-Tile/G-Tile

- Forward OCN transactions between GT/NT or DT/NT

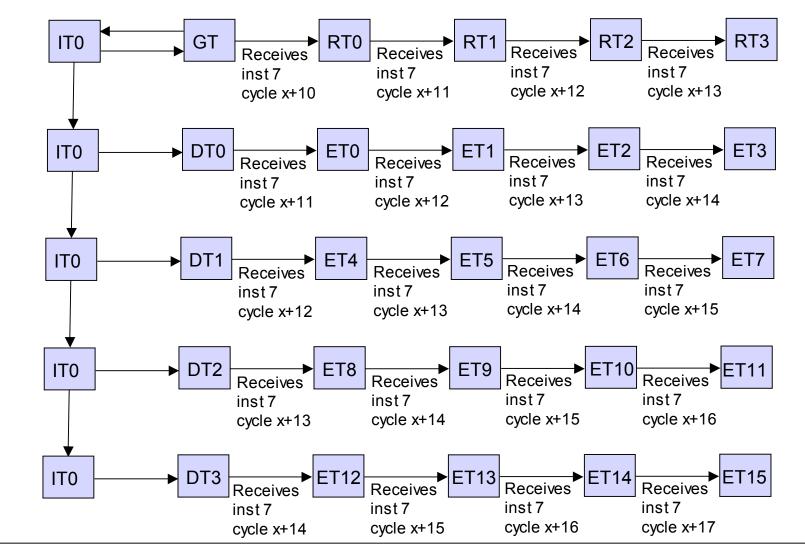

### Major I-Tile Structures

## Instruction Layout in a Maximal Block

## Instruction Fetch Pipeline

|     | Cycle 0                              | Cycle 1                                      | Cycle 2      | Cycle 3                       | Cycle 4                                          | Cycle 9                                              |                                                  |

|-----|--------------------------------------|----------------------------------------------|--------------|-------------------------------|--------------------------------------------------|------------------------------------------------------|--------------------------------------------------|

| GT  | ITLB<br>Iookup<br>I-\$ Tag<br>Iookup | Hit/Miss<br>detection<br>Frame<br>allocation | Fetch slot 0 | Fetch slot 1                  | Fetch slot 2                                     | <br>Fetch slot 7                                     |                                                  |

|     | Ισοκάρ                               |                                              |              |                               |                                                  |                                                      |                                                  |

|     |                                      |                                              |              | Cycle 3                       | Cycle 4                                          | Cycle 9                                              | Cycle 10                                         |

| IT0 |                                      |                                              |              | R/W slot 0<br>Fetch slot<br>0 | R/W slot 1<br>Fetch slot 1<br>Dispatch<br>slot 0 | <br>R/W slot 6<br>Fetch slot 6<br>Dispatch<br>slot 5 | R/W slot 7<br>Fetch slot 7<br>Dispatch<br>slot 6 |

|     |                                      |                                              |              |                               | -                                                |                                                      |                                                  |

|     |                                      |                                              |              |                               | Cycle 4                                          | Cycle 9                                              |                                                  |

| IT1 |                                      |                                              |              |                               | R/W slot 0<br>Fetch slot<br>0                    | <br>R/W slot 5<br>Fetch slot 5<br>Dispatch<br>slot 4 |                                                  |

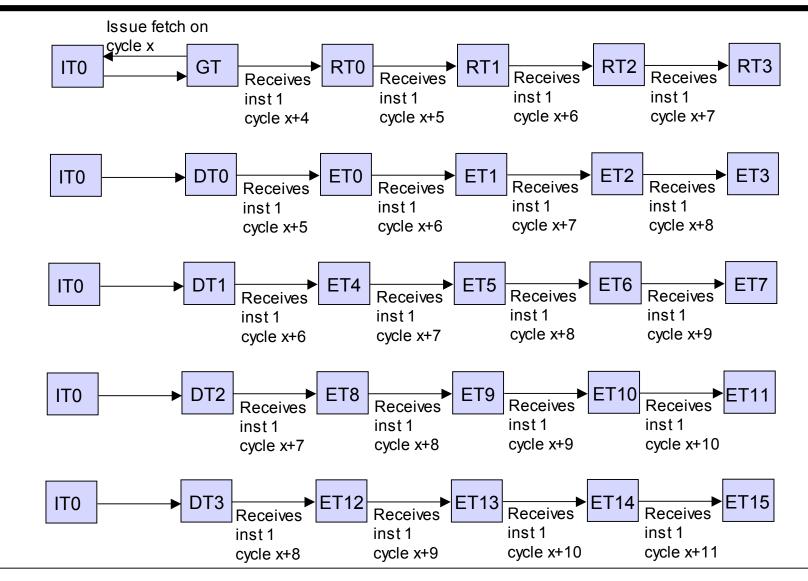

## Instruction Dispatch Timing Diagram

June 4, 2005

## Instruction Dispatch Timing Diagram

## Instruction Dispatch Timing Diagram

June 4, 2005

## Instruction Refill

- Receive refill id and block physical address from GRN input

- Request 128 bytes of inst. from memory hierarchy

- Send out 2 OCN read requests

- Buffer received inst. in refill buffer

- Report refill completion on GSN output when

- 128 bytes of inst. have been received

- Completion has been received on GSN input

- Write inst. into SRAM when dispatched from refill buffer

## Register Accesses and Operand Routing

#### **ISCA-32** Tutorial

Karu Sankaralingam

Department of Computer Sciences The University of Texas at Austin

### **R-Tile and OPN Location and Connections**

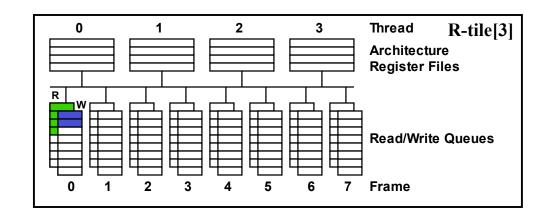

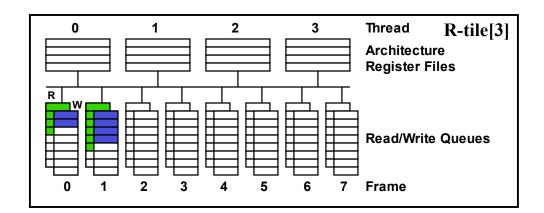

# Major R-Tile Responsibilities

- Maintain architecture state, commit register writes

- 512 registers total

- 128 registers per thread, interleaved across 4 tiles

- 32 registers/thread \* 4 threads = 128 registers per tile

- Process read/write instructions for each block

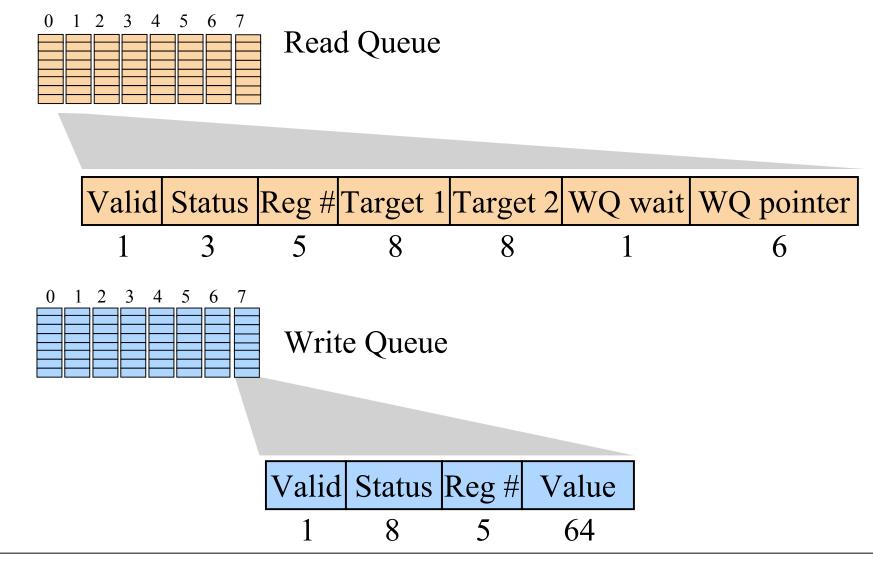

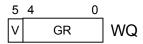

- 64 entry Read Queue (RQ), 8 blocks, 8 reads in each

- 64 entry Write Queue (WQ), 8 blocks, 8 writes in each

- Forward inter-block register values

- Detect per-block and per-tile register write completion

- Detect exceptions that flow to register writes

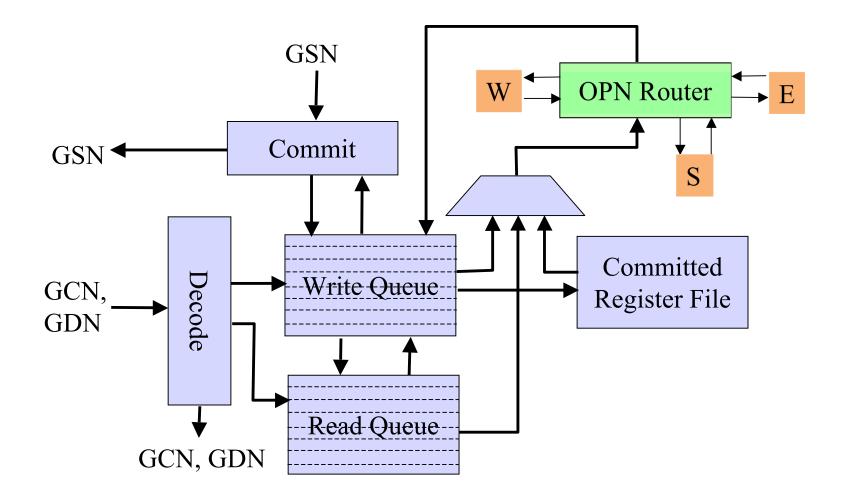

#### Major Structures in the R-tile

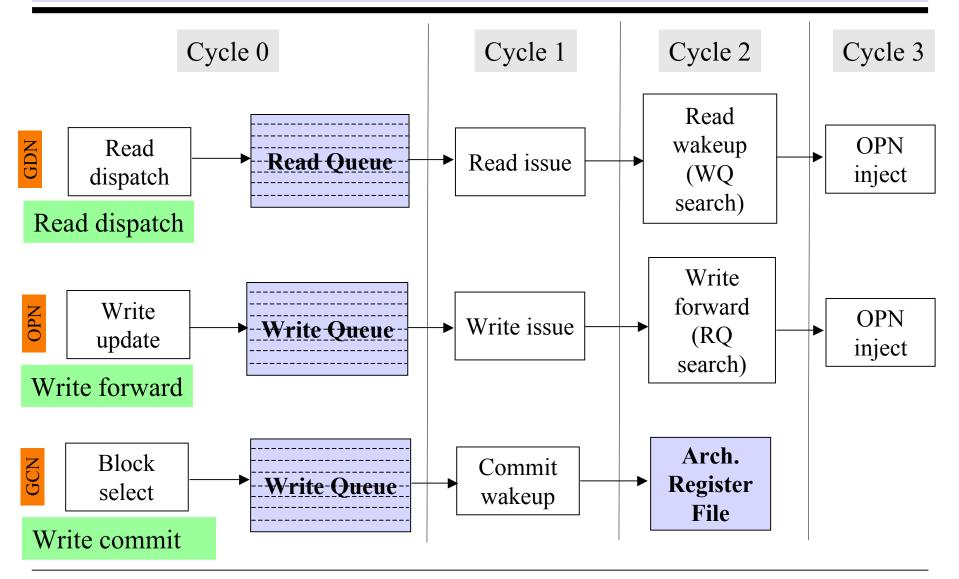

#### Pipeline diagrams: Register Read and Write

June 4, 2005

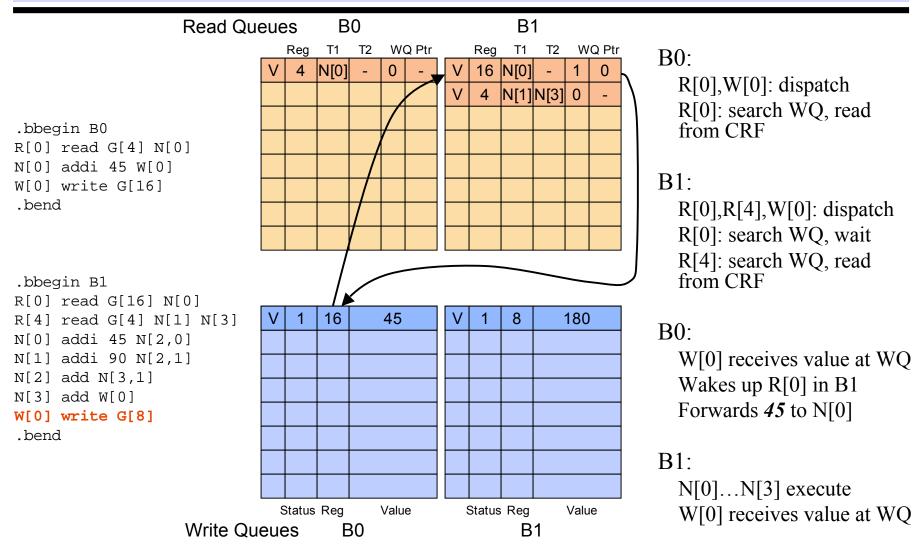

## Register Forwarding: RQ and WQ contents

## Register Forwarding Example

#### Block completion: Commit unit

June 4, 2005

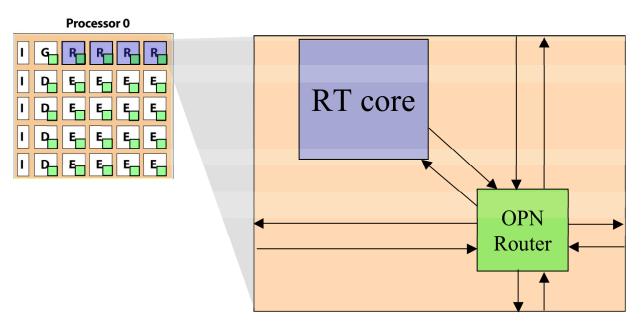

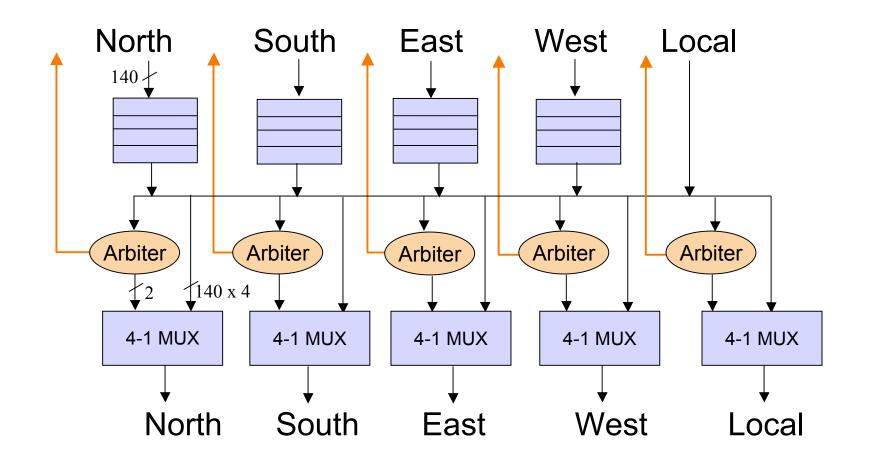

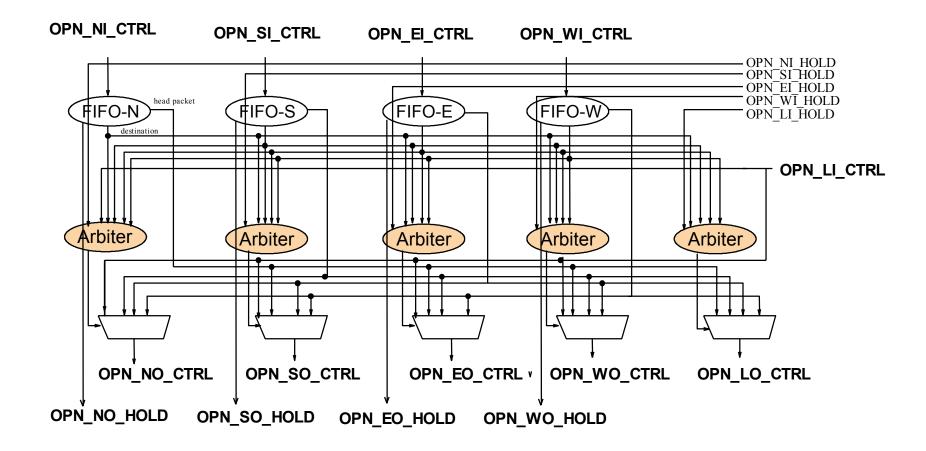

# Major OPN Responsibilities and Attributes

- Wormhole-routed network connecting 25 tiles

- 4 entry FIFO flit buffers in each direction

- Fixed packet length; 2 flits

- On-off flow control: 1-bit hold signal

- Dimension order routing (Y-X)

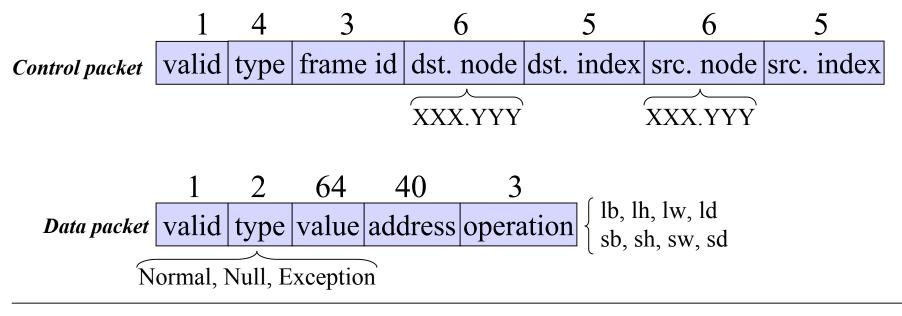

#### **OPN Packet Format**

- One control packet followed by one data packet in next cycle

- Dedicated wires for control/data

- Control packet

- Contains routing information

- Enables early wakeup and fast bypass in ET

0 - Generic transfer or reply

1 - Load

2 - Store

**Control Packet Types**

- 4 PC read

- 5 PC write

- 14 Special register read

- 15 Special register write

## **OPN Router Schematic**

## **Operand Network Properties**

- Directly integrated into processor pipeline

- Hold signal stalls tile pipelines (back pressure flow control)

- FIFOs flushed with processor flush wave

- Deadlock avoidance

- On-off flow control

- Dimension order routing

- Guaranteed buffer location for every packet

- Tailored for operands

- [Taylor et al. 2003, Sankaralingam et al. 2003]

#### Issue Logic and Execution

#### **ISCA-32** Tutorial

Premkishore Shivakumar

Department of Computer Sciences The University of Texas at Austin

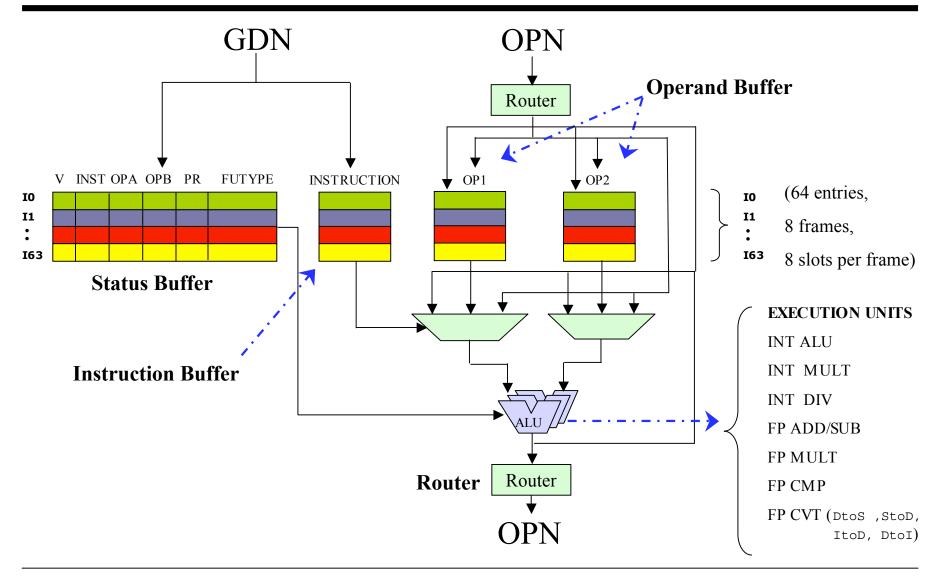

#### **E-Tile Location and Connections**

## Networks Used by E-Tile

- **OPN** Operand Network

- Transmit register values from/to R-tiles

- Transmit operands from/to other E-tiles

- Transmit load/store packets from/to D-tiles

- **GDN** Global Dispatch Network

- Receive instructions from I-tile, and the dispatch commands from G-tile

- Through a D-tile or a neighboring E-tile

- GCN Global Control Network

- Receive commit, flush commands originating at G-tile

- From a D-tile or a neighboring E-tile

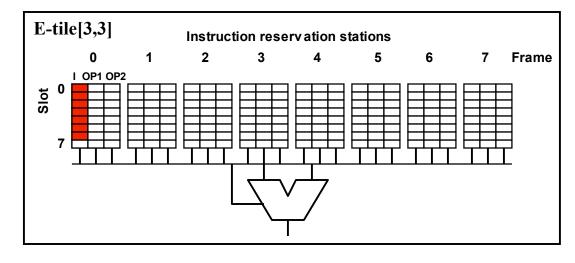

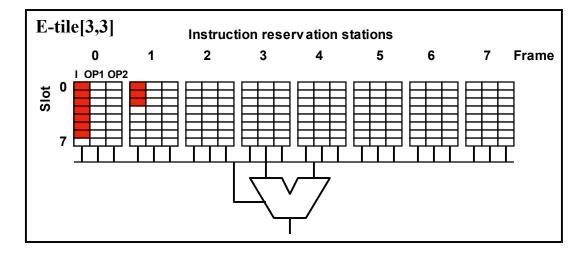

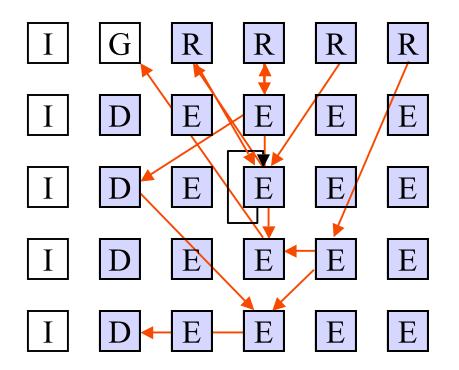

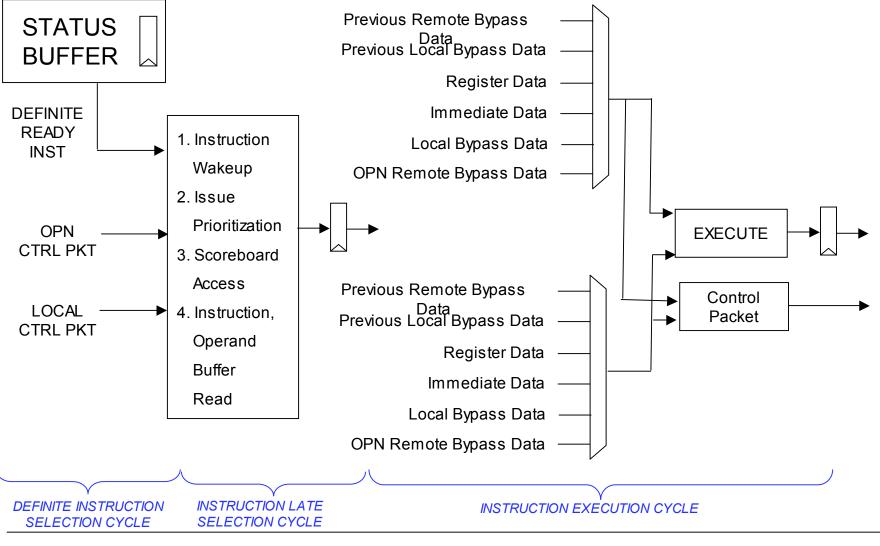

# Major E-Tile Responsibilities

- Buffer Instructions and Operands

- Local reservation stations for instruction and operand management

- Instruction Wakeup and Select

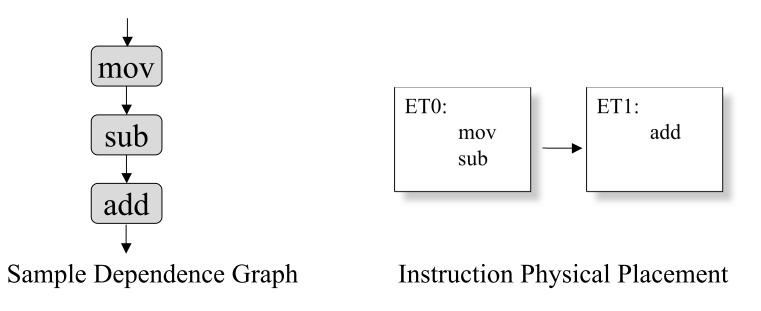

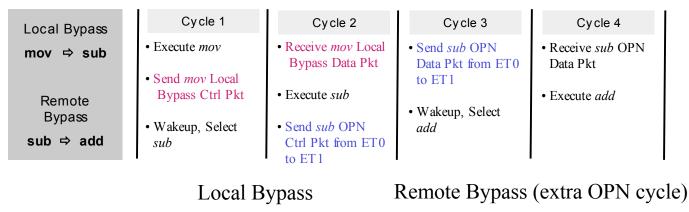

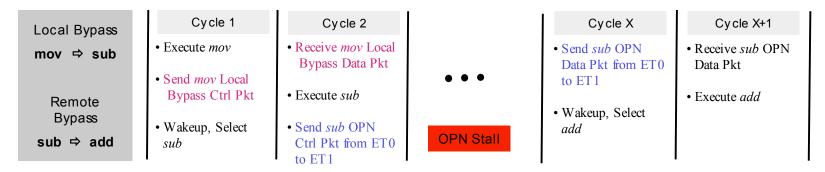

- Operand Bypass

- Local operand bypass to enable back-to-back local dependent instruction execution

- Remote operand bypass with one extra cycle of OPN forwarding latency per hop

- Instruction Target Delivery

- Instructions with multiple local and/or remote targets

- Successive local or remote targets in consecutive cycles

- Concurrently deliver a remote and a local target

- Predication Support

- Predicate-based conditional execution

- Hardware predicate OR-ing

- Exception and Null

- Exception generation: divide by zero exception, NULL instruction

- Exception and null tokens propagated in dataflow manner to register writes, stores

- Flush and Commit

- Clear block state (pipeline registers, status buffer etc.)

# E-Tile High Level Block Diagram

## Functional Unit Latencies in the E-Tile

| Functional Unit    | Latency        | Implementation |  |

|--------------------|----------------|----------------|--|

| Integer ALU        | 1              | Synopsys IP    |  |

| Integer Multiplier | 3 (Pipelined)  | Synopsys IP    |  |

| Integer Divider    | 24 (Iterative) | Synopsys IP    |  |

| FP Add / Sub       | 4 (Pipelined)  | Synopsys IP    |  |

| FP Multiplier      | 4 (Pipelined)  | Synopsys IP    |  |

| FP Comparator      | 2 (Pipelined)  | Synopsys IP    |  |

| FP DtoI Convert    | 2 (Pipelined)  | Synopsys IP    |  |

| FP ItoD Convert    | 3 (Pipelined)  | Synopsys IP    |  |

| FP StoD Convert    | 2 (Pipelined)  | UT TRIPS IP    |  |

| FP DtoS Convert    | 3 (Pipelined)  | UT TRIPS IP    |  |

#### Issue Prioritization Among Ready Instructions

Reservation stations at one E-Tile

- Instructions can execute out-of-order

- Issue prioritization among ready instructions

- Scheduler assigns slots for block instructions

- Slot based instruction priority within a block

#### Issue Prioritization Among Ready Instructions

Reservation stations at one E-Tile

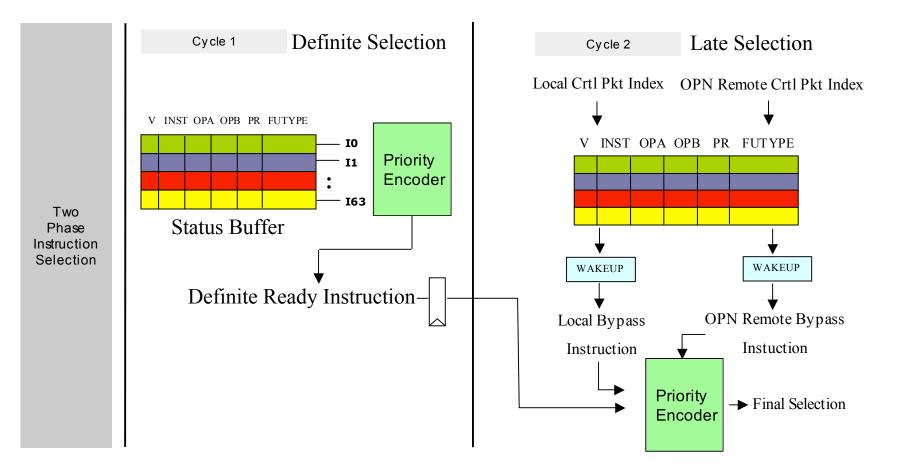

#### Two Phase Instruction Selection

- Priority Encoder uses Issue Prioritization Policy

- Wakeup: Back-to-back operand delivery, and two bypassed operands in the same cycle

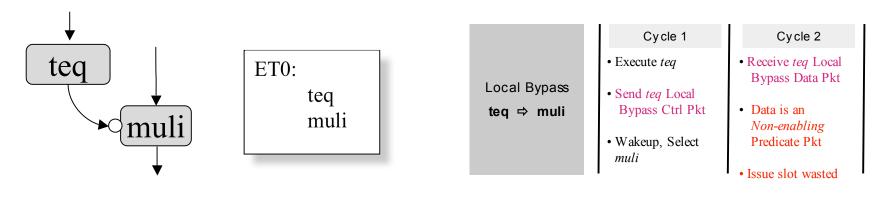

## Basic Operand Local & Remote Bypass

# Bypass: Sources of Pipeline Bubbles

• OPN stall due to network congestion

- Bypassed operand data is a *non-enabling* predicate

- -Detected in execute stage after receiving bypassed data => Issue slot wasted

- -Similar pipeline bubble due to invalid bypassed OPN data packet

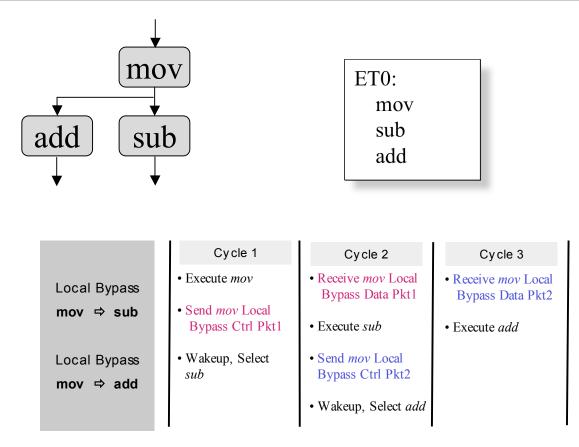

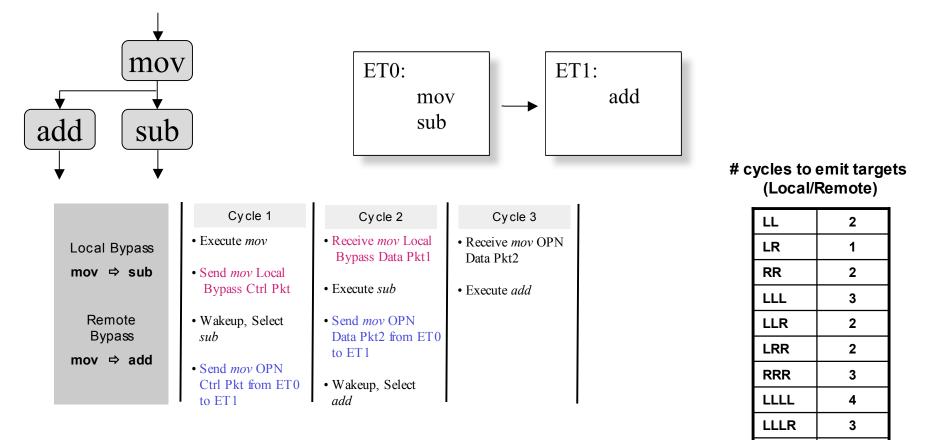

## Target Delivery: Multiple Local Targets

- Successive local targets delivered in consecutive cycles

- Successive remote targets also delivered in consecutive cycles (extra OPN forward cycle)

## Concurrent Local & Remote Target Delivery

- Instruction local and remote target can be sent concurrently

- *mov3*, *mov4* instructions have 3 and 4 targets respectively, used to fanout operands to multiple children

2

3

4

LLRR LRRR

RRRR

## Primary Memory System

#### **ISCA-32** Tutorial

Simha Sethumadhavan

Department of Computer Sciences The University of Texas at Austin

#### **D-Tile Location and Connections**

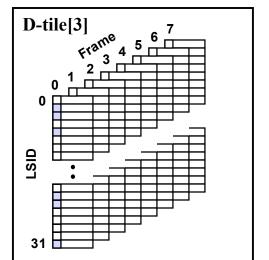

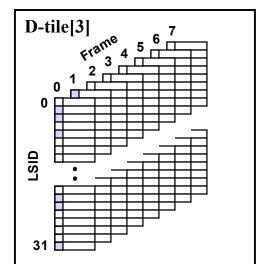

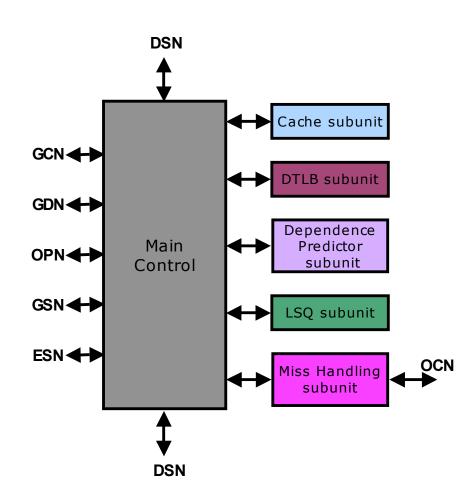

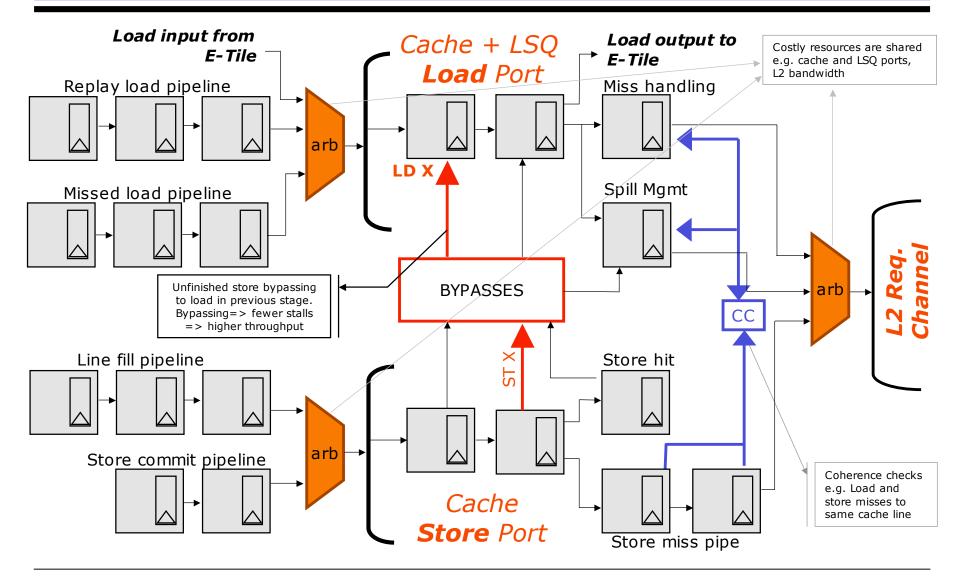

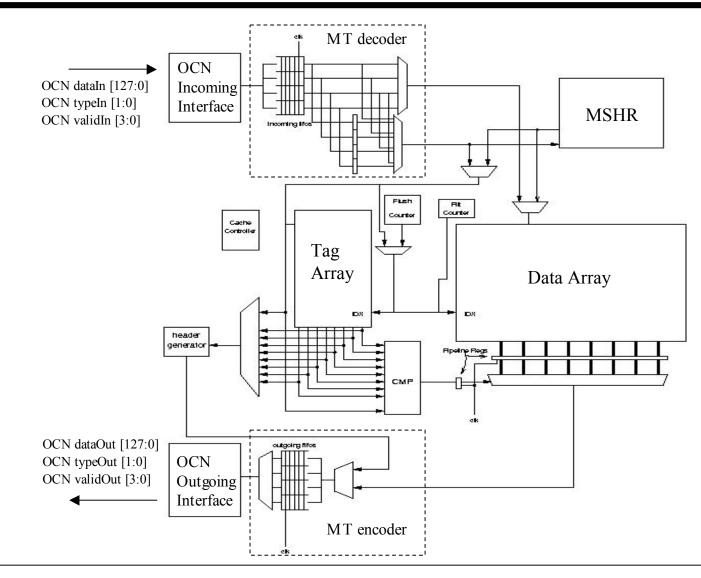

# Major D-Tile Responsibilities

- Provide D-cache access for arriving loads and stores

- Perform address translation with DTLB

- Handle cache misses with MSHRs

- Perform dynamic memory disambiguation with load/store queues

- Perform dependence prediction for aggressive load/store issue

- Detect per-block store completion

- Write stores to caches/memory upon commit

- Store merging on L1 cache misses

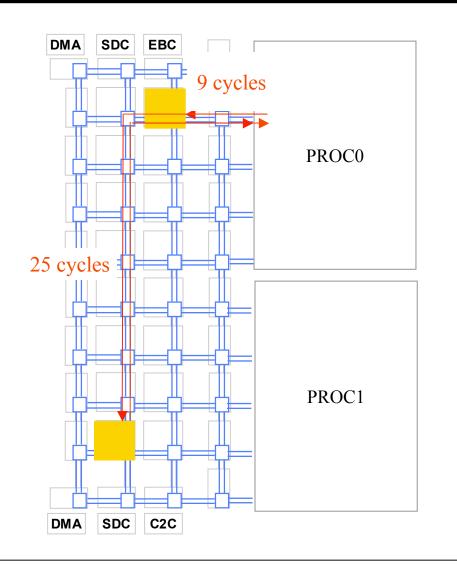

## Primary Memory Latencies

- Data cache is interleaved on a cache line basis (64 bytes)

- Instruction placement affects load latency

- Best case load-to-use latency: 5 cycles

- Worst case load-to-use latency: 17 cycles

- Loads favored in E-tile column adjacent to the D-tiles

- Deciding row placement is difficult

- Memory access latency: Three components

- From E-Tile (load) to D-Tile (a)

- D-Tile access (this talk) (b)

- From D-Tile back to E-Tile (load target) ⓒ

#### Major Structures and Sizes in the D-Tile

- Caches

- 8KB, 2-way, 1R and 1W port

- 64 byte lines, LRU, Virtually indexed, physically tagged,

- Write-back, Write-no-allocate

- DTLB

- 16 entries, 64KB to 1TB pages

- Dependence Predictor

- 1024 bits, PC based hash function

- Load Store Queues

- 256 entries, 32 loads/stores per block, single ported

- Miss Handling

- 16 outstanding load misses to 4 cache lines

- Support for merging stores up to one full cache line

#### Load Execution Scenarios

| TLB  | Dep. Pr       | LSQ  | Cache | Response                                                                          |

|------|---------------|------|-------|-----------------------------------------------------------------------------------|

| Miss | -             | -    | -     | Report TLB Exception                                                              |

| Hit  | Wait<br>(Hit) | _    | -     | Defer load until all prior stores are received. Non deterministic latency         |

| Hit  | Miss          | Miss | Hit   | Forward data from L1 Cache                                                        |

| Hit  | Miss          | Miss | Miss  | Forward data from L2 Cache (or memory)<br>Issue cache fill request (if cacheable) |

| Hit  | Miss          | Hit  | Hit   | Forward data from LSQ                                                             |

| Hit  | Miss          | Hit  | Miss  | Forward data from LSQ<br>Issue cache fill request (if cacheable)                  |

# Load Pipeline

• Common case: 2 cycle load hit latency

| TLB Hit   | Cycle 1            | Cycle 2    |

|-----------|--------------------|------------|

| DP Miss   | Access             | Load Reply |

| Cache Hit | Cache,<br>TLB, DP, |            |

| LSQ Miss  | and LSQ            |            |

- For LSQ hits, load latency varies between 4 to n+3 cycles, where n is size of the load in bytes

- Stalls all pipelines except forwarding stages (cycles 2 and 3)

| TLB Hit           | Cycle 1             | Cycle 2              | Cycle 3            | Cycle 4    |

|-------------------|---------------------|----------------------|--------------------|------------|

| DP miss           | Access<br>Cache,    | Identify<br>Store in | Read<br>Store Data | Load Reply |

| Cache<br>Hit/Miss | TLB, DP,<br>and LSQ | the LSQ              |                    |            |

| LSQ Hit           |                     | Stall Pipe           | Stall Pipe         |            |

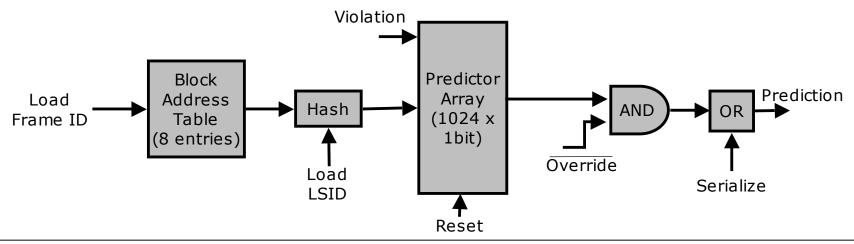

## **Dependence** Prediction

- Prediction at memory side (not at issue)

- New invention because of distributed execution

- Properties

- PC-based, updated on violation

- Only loads access the predictor, loads predicted dependent are *deferred*

- *Deferred* loads are woken up when *all* previous stores have arrived

- Reset periodically (flash clear) based on number of blocks committed

- Dependence speculation is configurable: Override, Serial, Regular

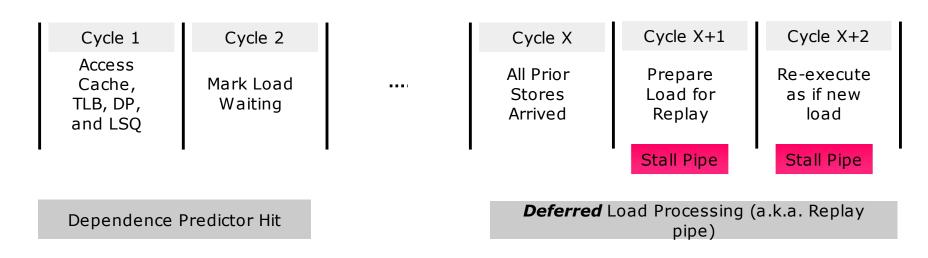

# Deferred Load Pipeline

- Deferred loads are woken up when all prior stores have arrived at D-tiles

- Loads between two consecutive stores can be woken up out-of-order

- Deferred loads are re-injected into the main pipeline, as if they were new load

- During this phase, loads get the value from dependent stores, if any

- Pipeline stall

- When deferred load in cycle X+2 cannot be re-injected into the main pipeline

- Load cannot be prepared in cycle X+1 because of resource conflicts in the LSQ

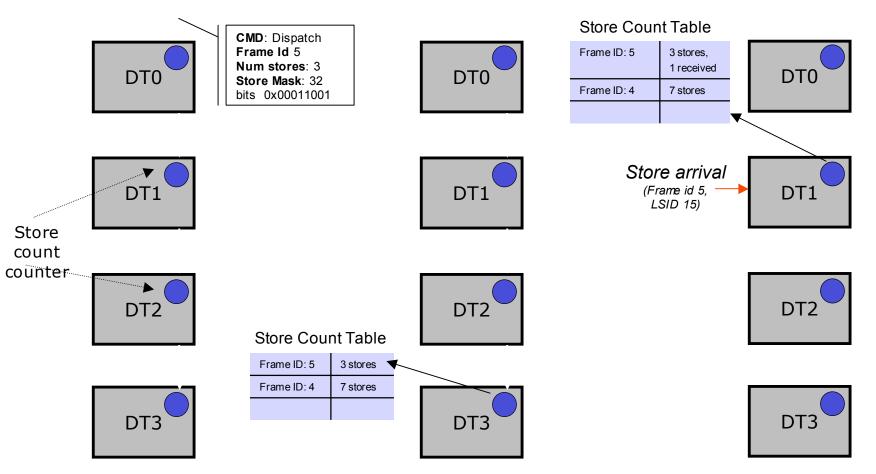

## Store Counting

GDN

At block dispatch, each DT receives and records information on stores in the dispatched block June 4, 2005 Each DT records store counts and store mask (in the LSQ). Store mask (32 bits) identifies the store instructions in a block

instructions in a block UT-Austin TRIPS Tutorial On store arrival, the received store count is updated at local tile and store arrival is passed on to other tiles (next slide) 141

#### **Block Store Completion Detection**

# Store Commit Pipeline

|                 | Cycle 1                                  | Cycle 2                                         | Cycle 3                 | Cycle 4                     | Cycle 5                                 |

|-----------------|------------------------------------------|-------------------------------------------------|-------------------------|-----------------------------|-----------------------------------------|

| Store<br>Commit | Pick<br>Store<br>to commit<br>Stall Pipe | Read<br>Store<br>data from<br>LSQ<br>Stall Pipe | Access<br>cache<br>tags | Check for<br>hit<br>or miss | Write to<br>Cache or<br>Merge<br>buffer |

- Stores are committed in LSID and block order at each D-tile

- Written into L1 cache or bypassed on a cache miss

- One store committed per D-tile per cycle

- Up to four stores total can be committed every cycle, possibly out-of-order

- T-morph: Store commits from different threads are not interleaved

- On a cache miss, stores are inserted into the merge buffer

- Commit pipe stalls when cache ports are busy

- Fills from missed loads take up cache write ports

# Load and Store Miss Handling

- Load Miss Operation

- Cycle 1: Miss determination

- Cycle 2: MSHR allocation and merging

- Cycle 3: Requests sent out on OCN, if available

- Load Miss Return

- Cycle 1: Wake up all loads waiting on incoming data

- Cycle 2: Select one load; data for the load miss starts arriving

- Cycle 3: Prepare load and re-inject into main pipeline, if unblocked

- Store Merging

- Attempts to merge consecutive writes to same line

- Snoops on all incoming load misses for coherency

- Resources are shared across threads

# D-Tile Pipelines Block Diagram

### Memory System Design Challenges

- Optimizing and reducing the size of the LSQ

- Prototype LSQ size exceeds data cache array size

- Further optimization of memory-side dependence prediction

- Prior state of the art is done at instruction dispatch/issue time

- Scaling and decentralizing the Data Status Network (DSN)

D-Tile Roadmap 😳

# Secondary Memory System

#### **ISCA-32** Tutorial

Changkyu Kim

Department of Computer Sciences The University of Texas at Austin

### M-Tile Location and Connections

## M-Tile Network Attributes

- Total 1MB on-chip memory capacity

- Array of 16 64KB M-Tiles

- Connected by specialized on-chip network (OCN)

- High bandwidth

- A peak of 16 cache accesses per cycle

- 68 GB/sec to the two processor cores

- Low latency for future technologies

- Non-uniform (NUCA) level-2 cache

- Configuration

- Scratchpad / Level-2 cache modes on a per-bank basis

- Configurable address mapping

- Shared L2 cache / Private L2 cache

## Non-Uniform Level-2 Cache (NUCA)

- Non-uniform access latency

- Closer bank can be accessed faster

- Designed for wire-dominated future technologies

- No global interconnect

- Connected by switched network

- Can fit large number of banks with small area overhead

- Allows thousands of in-flight transactions

- Network capacity = 2100 flits

- Maximize throughput

## Multiple Modes in TRIPS Secondary Memory

| L2 |  |

|----|--|

|    |  |

: M-Tile configured as a level-2 Cache

: M-Tile configured as a scratchpad memory

### Major Structures in the M-Tile

• Error checking and handling

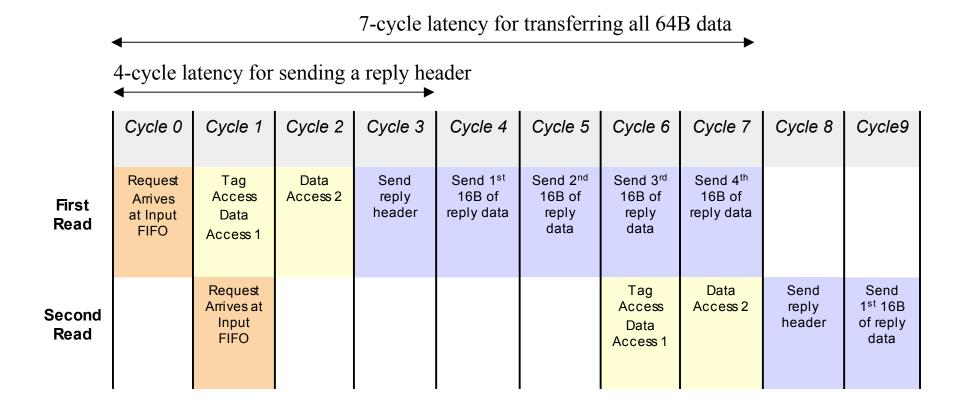

## Back-to-Back Read Pipeline

Seamless Data Transfer (6.8GB/sec)

# Read Miss Pipeline

## Chip- and System-Level Networks and I/O

#### **ISCA-32** Tutorial

Paul Gratz

Department of Computer Sciences The University of Texas at Austin

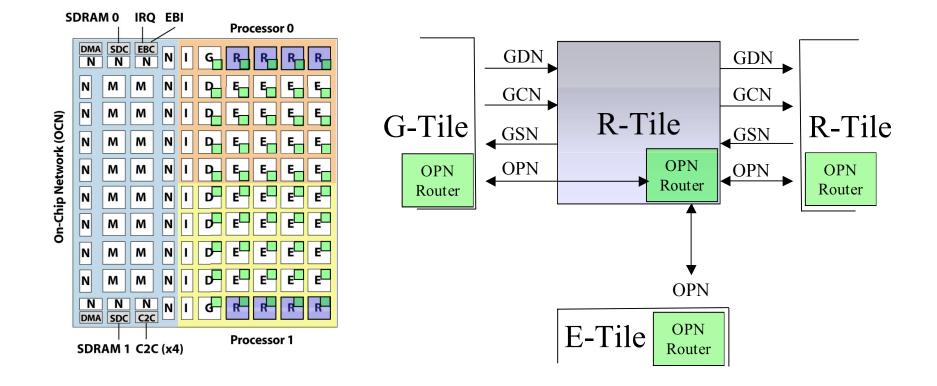

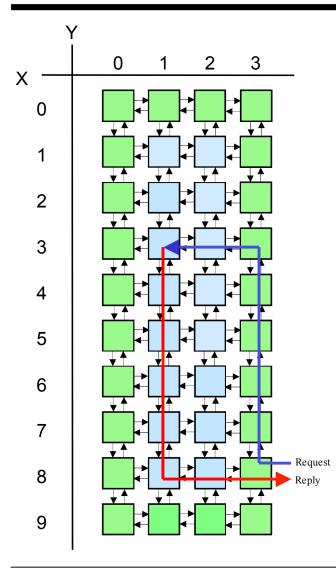

### **OCN Location and Connections**

## Goals and Requirements of the OCN

- Fabric for interconnection of processors, memory and I/O

- Handle multiple types of traffic:

- Routing of L1 and L2 cache misses

- Memory requests

- Configuration and data register reads/writes by external host

- Inter-chip communication

- OCN Network Attributes

- Flexible mapping of resources

- Deadlock free operation

- Performance (16 Client Links 6.8GB/sec per link)

- Guaranteed delivery of request and reply

# OCN Protocol

- Flexible mapping of resources

- System address mapping tables are runtime re-configurable to allow for runtime re-mapping between L2 cache banks and scratchpad memory banks

- Deadlock Avoidance

- Dimension order routed network (Y-X)

- Four virtual channels used to avoid deadlock

- Performance

- Links are 128 bit wide in each direction

- Credit-based flow control

- One cycle per hop plus cycle at network insertion

- 68 GB/sec at processor interfaces

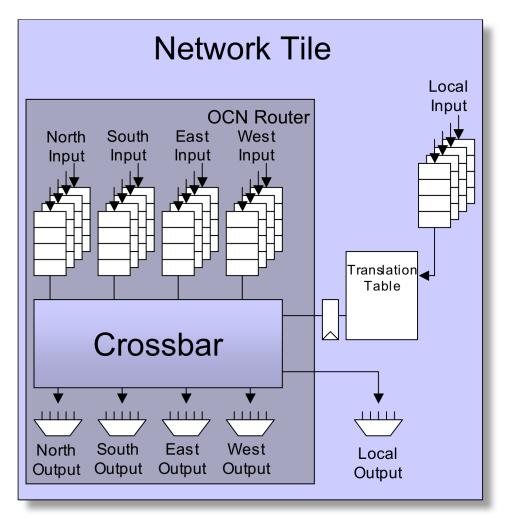

# N-Tile Design

Goals

•

- Router for OCN packets

- System address to network address translation

- Configurable L2 network addresses

- One cycle per hop latency

- Attributes

- Composed of OCN router with translation tables on local input

- Portions of the system address index into translation tables

- Translation tables configured through memory mapped registers

- Error back on invalid addresses

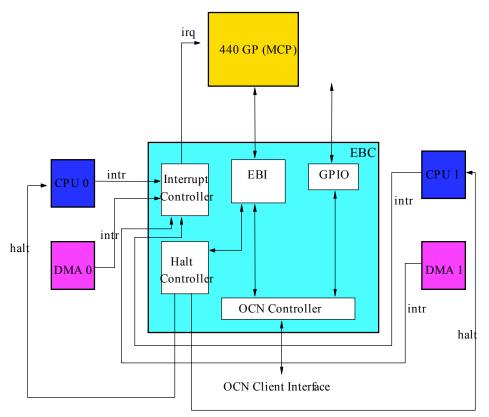

# I/O Tiles

EBC Tile

- Provides interface between board-level

PowerPC 440 GP chip and the TRIPS chip

- Forwards interrupts to the 440 GP's service routines

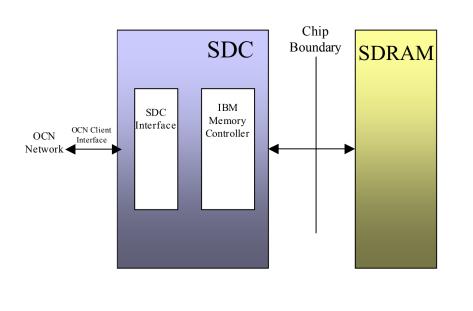

- SDC Tile

- Contains IBM SDRAM Memory Controller

- Error detection, swap support and address remapping added

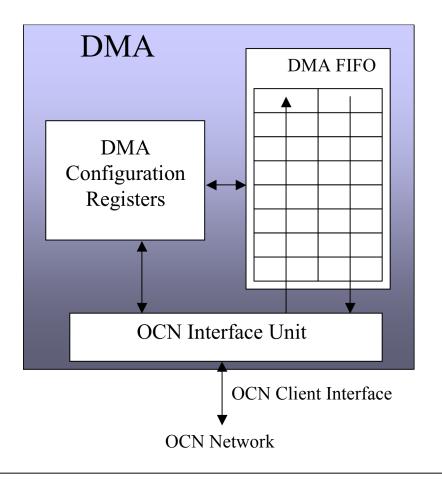

- DMA Tile

- Supports multi-block and scatter/gather transfers

- Buffered to optimize traffic

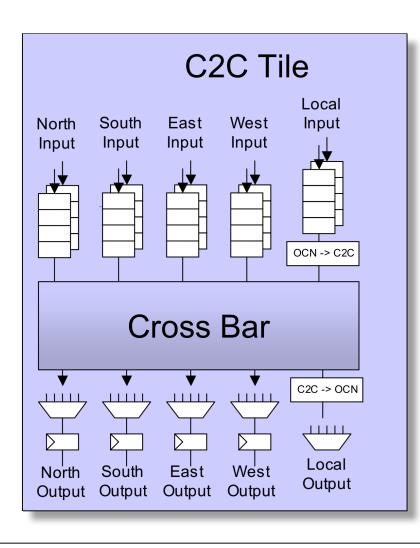

- C2C Tile

## C2C Tile Design Considerations

- C2C Goals

- Extend OCN fabric across multiple chips

- Provide flexible extensibility

- C2C Attributes

- C2C network protocol similar to OCN except:

- 64 bit wide

- 2 virtual channels

- Operates at up to 266MHz

- Clock speed configurable at boot

- Source synchronous off-chip links

- Multiple clock domains with resynchronization

## C2C Network

- Latencies:

- L2 Hit Latency: 9 27 cycles

- L2 Miss Latency: 26 44 cycles (+ SDRAM Access time)

- L2 Hit Latency (adjacent chip):

33 63 cycles

- L2 Miss Latency (adjacent chip): 50 – 78 cycles (+SDRAM)

- Each additional C2C hop adds 8 cycles in each direction

- Bandwidth:

- OCN Link: 6.8 GB/sec

- One processor to OCN: 34 GB/sec

- Both processors to OCN: 68 GB/sec

- Both SDRAMs: 2.2 GB/sec

- C2C Link: 1.7 GB/sec

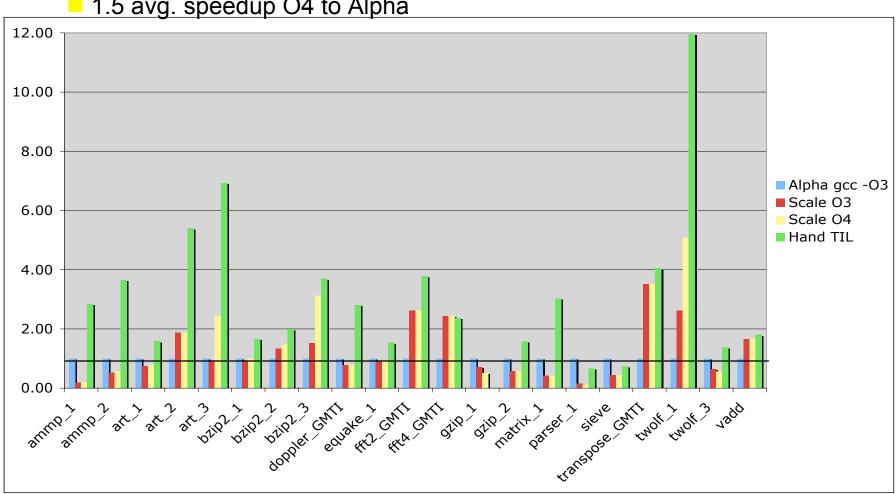

# Compiler Overview

#### **ISCA-32** Tutorial

Kathryn McKinley

Department of Computer Sciences The University of Texas at Austin

# Compiler Challenges

"Don't put off to runtime what you can do at compile time." Norm Jouppi, May 2005.

- Block constraints & compiler scheduling

- Makes the hardware simpler

- Shifts work to compile time

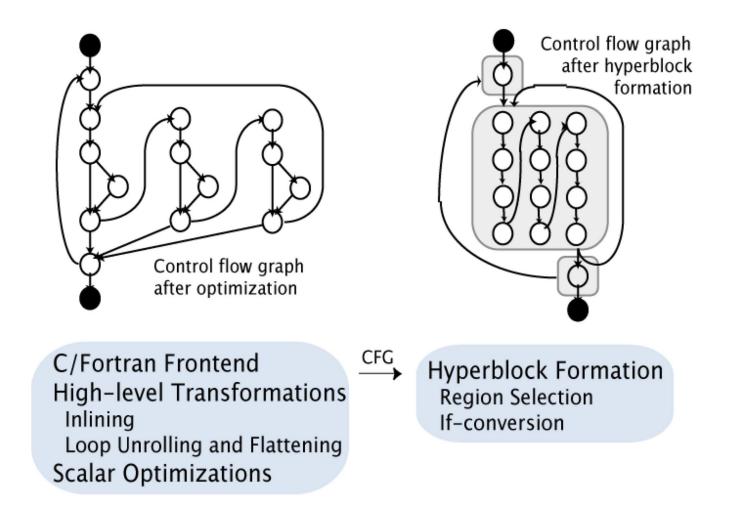

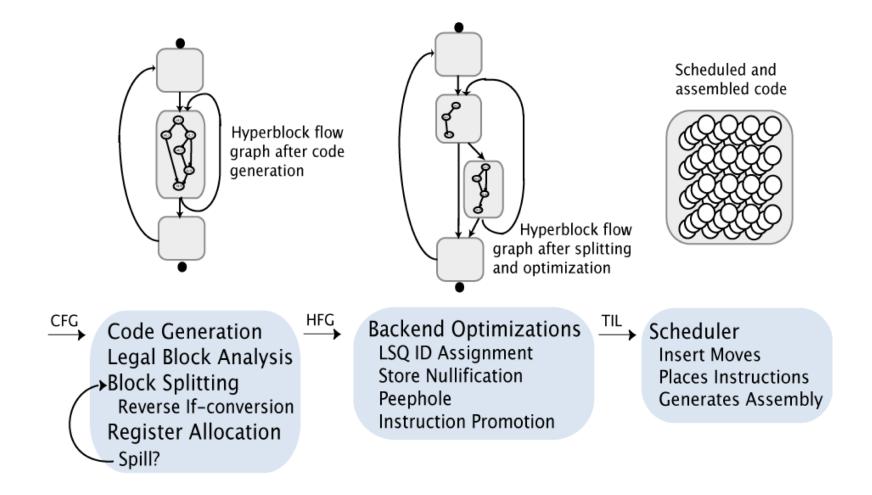

# Generating Correct, High Performance Code

- TRIPS specific compiler challenges

- EDGE execution model

- What's a TRIPS block?

- The compiler's job

- Correct code

- Satisfying TRIPS block constraints

- Optimized code

- Filling up TRIPS blocks with useful instructions

## **Block Execution**

# **TRIPS Block Constraints**

- Fixed size: 128 instructions

- Padded with no-ops if needed

- Simpler hardware: instruction size, I-cache design, global control

- **Registers**: 8 reads and writes to each of 4 banks (in addition to 128 instructions)

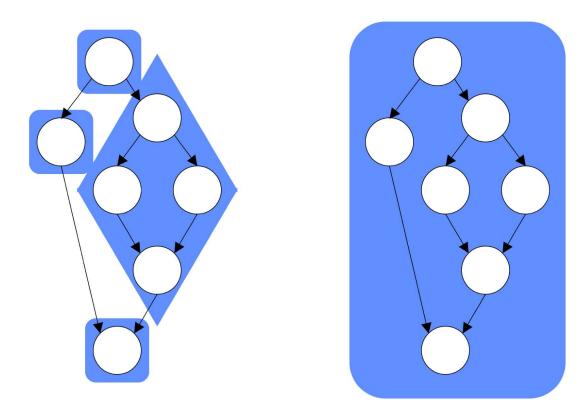

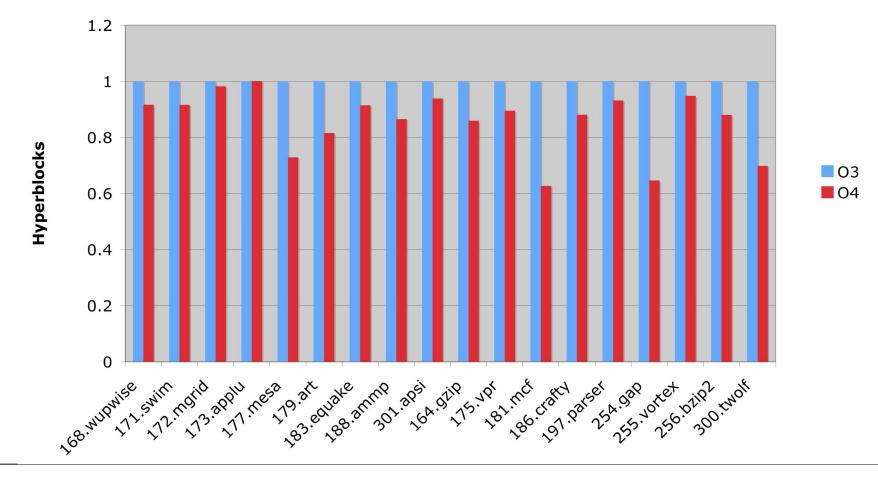

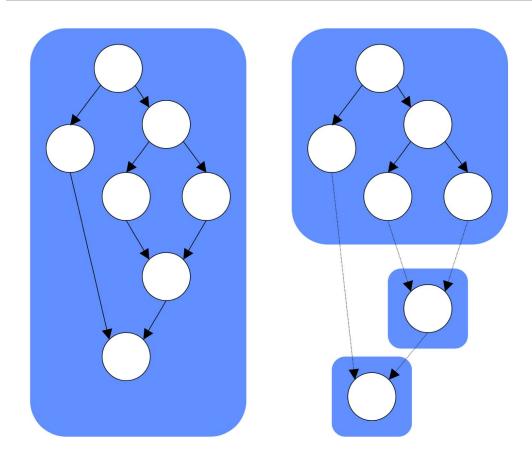

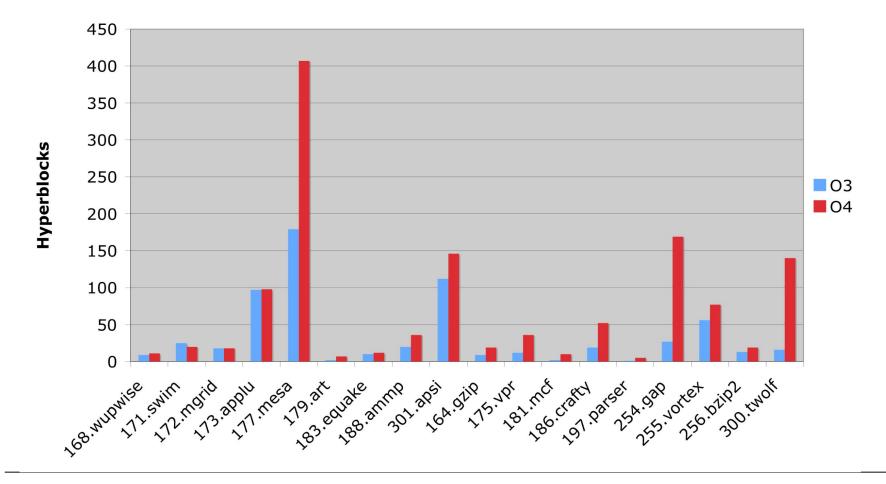

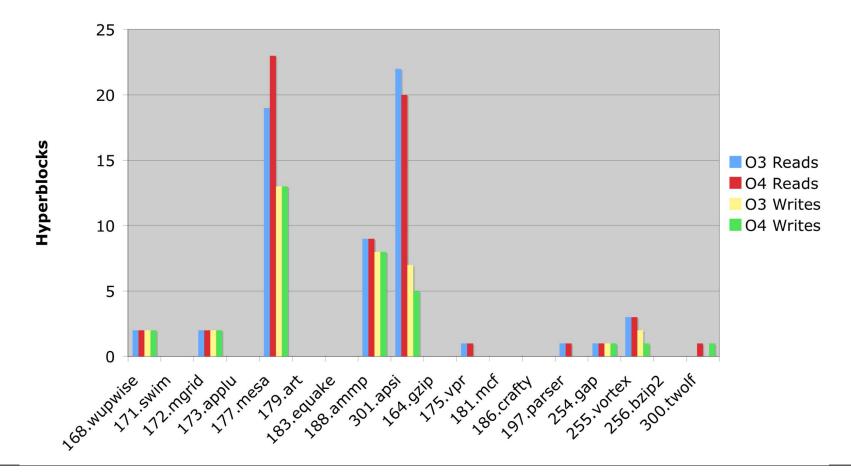

- Reduced buffering