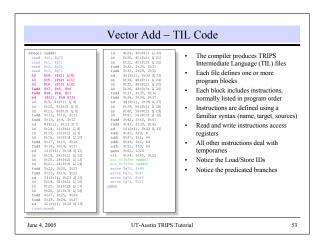

| RISC code                                                                                                                                                               | TIL (operand format)                                                                                                                                                                                                                      | TASL (target format)                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ld       R3, 4(R2)         add       R4, R1, R3         st       R4, 4(R2)         addi       R5, R4, 4(R2)         addi       R5, R4, #2         begz       R4, Block3 | .bbegin block1<br>read \$t1, \$g1<br>read \$t2, \$g2<br>ld \$t3, 4(\$t2)<br>add \$t4, \$t1, \$t3<br>st \$t4, 4(\$t2)<br>add1 \$t5, \$t4, 2<br>teqz \$t6, \$t4<br>b_t<\$t6> block3<br>b_f<\$t6> block2<br>write \$g5, \$t5<br>.bend block1 | [R1] \$g1 [2]<br>[R2] \$g2 [1] [4]<br>[1] 1d L[1] 4 [2]<br>[2] add [3] [4]<br>[3] mov [5] [6]<br>[4] st S[2] 4<br>[5] add1 2 [M1]<br>[6] teqz [7] [8]<br>[7] b_t block3<br>[8] b_f block2<br>[W1] \$g5 |

| Block outputs fixed<br>(3 in this example)                                                                                                                              | .bbegin block2                                                                                                                                                                                                                            |                                                                                                                                                                                                        |

| TA   | SL (targ | et format) |        |    | Objec | et Code |    |

|------|----------|------------|--------|----|-------|---------|----|

| [R1] | \$g1     | [2]        | v reg  | Т  | 1     | TO      | ]  |

| [R2] | \$g2     | [1] [4]    | v reg  | Т  | 1     | TO      | ]  |

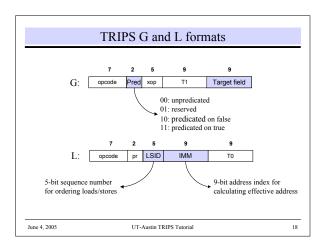

| [1]  | ld       | L[1] 4     | opcode | pr | LSID  | imm     | TO |

| [2]  | add      | [3] [4]    | opcode | pr | хор   | T1      | TO |

| [3]  | mov      | [5] [6]    | opcode | pr | хор   | T1      | TO |

| [4]  | st       | S[2] 4     | opcode | pr | LSID  | imm     | 0  |

| [5]  | addi     | 2 [W1]     | opcode | pr | хор   | imm     | TO |

| [6]  | teqz     | [7] [8]    | opcode | pr | хор   | T1      | TO |

| [7]  | b_t      | block3     | opcode | pr | exit  | offs    | et |

| [8]  | b_f      | block2     | opcode | pr | exit  | offs    | et |

| [W1] | \$g5     |            | v reg  |    |       |         |    |

| TASL (tar | get format) |         |        | Objec | t Code |      |

|-----------|-------------|---------|--------|-------|--------|------|

| [R1] \$g1 | [2]         | 1 00001 | [2     | ]     |        | ]    |

| [R2] \$g2 | [1] [4]     | 1 00010 | [1     | ]     | [4]    | ]    |

| [1] ld    | L[1] 4      | ld      | 00     | 00001 | 4      | [2]  |

| [2] add   | [3] [4]     | add     | 00     |       | [3]    | [4]  |

| [3] mov   | [5] [6]     | mov     | 00     |       | [5]    | [6]  |

| [4] st    | S[2] 4      | st      | 00     | 00010 | 4      |      |

| [5] addi  | 2 [W1]      | addi    | 00     |       | 2      | [W1] |

| [6] teqz  | [7] [8]     | teqz    | 00     |       | [7]    | [8]  |

| [7] b_t   | block3      | b       | 11 (t) | E0    | block3 | - PC |

| [8] b_f   | block2      | b       | 10 (f) | E1    | block2 | - PC |

| [W1] \$g5 |             | 1 00101 |        |       |        |      |

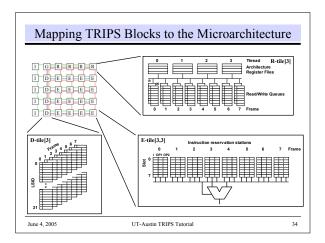

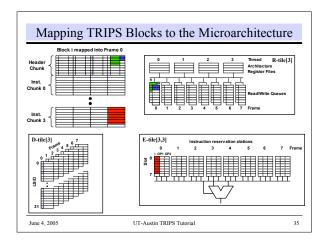

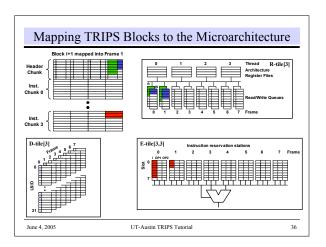

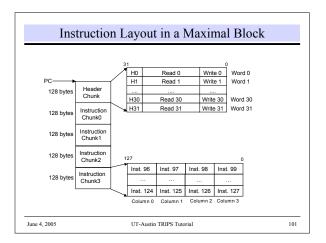

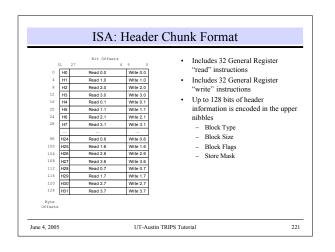

|              |                                                  | TRIPS Block Format                                                                                                                                                                                                                 |

|--------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ₽C→          | Header<br>Chunk                                  | <ul> <li>Each block is formed from two to five 128-byte program"chunks"</li> <li>Blocks with fewer than five chunks are</li> </ul>                                                                                                 |

| -            | Instruction<br>Chunk 0<br>Instruction<br>Chunk 1 | 128 Bytes       expanded to five chunks in the L1 I-cache         The header chunk includes a block header (execution flags plus a store mask) and register read/write instructions         Each instruction chunk holds 32 4-byte |

|              | Instruction<br>Chunk 2                           | 128 Bytes         • A maximally sized block contains 128 regular instructions, 32 read instructions, and 32 write instructions                                                                                                     |

|              | Instruction<br>Chunk 3                           | } 128 Bytes                                                                                                                                                                                                                        |

| June 4, 2005 |                                                  | UT-Austin TRIPS Tutorial 22                                                                                                                                                                                                        |

|                                             |                                            | Add – Pla                                    |                                        | <b>W</b> ICHO III                                                                                                            |

|---------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| ET0:<br>ld, mov3,<br>mov3, mov,<br>mov, mov | ET1:<br>mov3, ld,<br>mov, mov,<br>mov, mov | ET2:<br>mov, mov3,<br>ld, addi, addi,<br>mov | ET3:<br>mov, mov,<br>mov, mov3, ld     | <ul> <li>The scheduler<br/>analyzes each block<br/>dataflow graph</li> <li>It inserts fanout<br/>instructions, as</li> </ul> |

| ET4:<br>ld, ld, ld,<br>mov3, addi           | ET5:<br>ld, mov3,<br>mov3, fadd, sd        | ET6:<br>ld, fadd, ld, ld,<br>ld              | ET7:<br>ld, genu, addi                 | <ul> <li>needed</li> <li>It places the instructions within the block (they</li> </ul>                                        |

| ET8:<br>ld, ld, ld,<br>mov3, fadd, sd       | ET9:<br>ld, ld, ld, ld,<br>fadd            | ET10:<br>ld, fadd, fadd,<br>sd               | ET11:<br>fadd, fadd, sd,<br>tlt, bro_t | <ul><li>don't have to be in<br/>program order)</li><li>It produces<br/>assembly language<br/>files</li></ul>                 |

| ET12:<br>ld, fadd, fadd,<br>sd              | ET13:<br>ld, fadd, fadd,<br>sd             | ET14:<br>fadd, fadd, sd,<br>ld               | ET15:<br>fadd, fadd, sd,<br>bro_f      | <ul> <li>An instruction fires<br/>when its operands<br/>become available<br/>(regardless of<br/>position)</li> </ul>         |

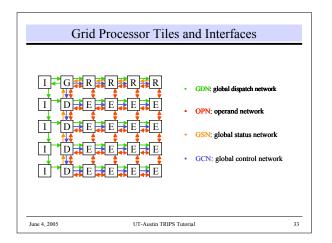

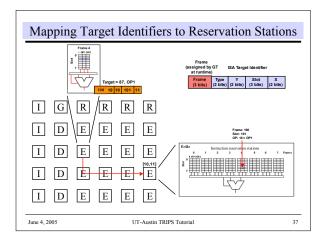

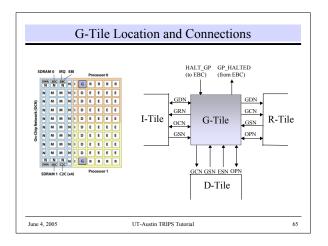

| I G<br>I D<br>I D<br>I D | R<br>E<br>E | R<br>E<br>E | R<br>E<br>E | R<br>E<br>E | Network (ESN)<br>Interface Ports<br>PENDING: Pending status of<br>external store requests and<br>spills in each thread<br>ERROR. Errors encountered for |

|--------------------------|-------------|-------------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| I D<br>I D               | E           | E           | E           | E           | ERROR: Errors encountered for<br>external store requests and<br>spills in each thread                                                                   |

|                          | Deliv       | ers ext     | ernal st    | ore pendi   | ng and error status from D-tiles                                                                                                                        |

| June 4, 2005             |             |             | U           | T-Austin TF | IPS Tutorial                                                                                                                                            |

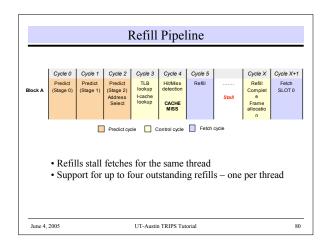

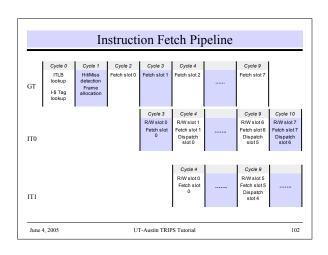

|         |                      |                      |                                           | Fotob                                        | Dina                                         | lina                 |                      |                      |                 |    |

|---------|----------------------|----------------------|-------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------|----------------------|----------------------|-----------------|----|

|         |                      |                      |                                           | reich                                        | Pipe                                         | ime                  |                      |                      |                 |    |

|         | Cycle 0              | Cycle 1              | Cycle 2                                   | Cycle 3                                      | Cycle 4                                      | Cycle 5              | Cycle 6              | Cycle 7              | Cycle 8         |    |

| Block A | Predict<br>(Stage 0) | Predict<br>(Stage 1) | Predict<br>(Stage 2)<br>Address<br>Select | TLB<br>lookup<br>l-cache<br>lookup           | Hit/Miss<br>detection<br>Frame<br>allocation | Fetch<br>SLOT 0      | Fetch<br>SLOT 1      | Fetch<br>SLOT 2      | Fetch<br>SLOT 3 |    |

| Block B |                      |                      |                                           |                                              |                                              | Predict<br>(Stage 0) | Predict<br>(Stage 1) | Predict<br>(Stage 2) | Stall           |    |

|         |                      |                      |                                           |                                              |                                              |                      |                      |                      |                 | -  |

| 5       | Cycle 9              | Cycle 10             | Cycle 11                                  | Cycle 12                                     | Cycle<br>13                                  | Cycle 14             | Cycle 15             | Cycle 16             | Cycle 17        |    |

|         | Fetch<br>SLOT 4      | Fetch<br>SLOT 5      | Fetch<br>SLOT 6                           | Fetch<br>SLOT 7                              |                                              |                      |                      |                      |                 |    |

|         | Stall                | Address<br>Select    | TLB<br>lookup<br>l-cache<br>lookup        | Hit/Miss<br>detection<br>Frame<br>allocation | Fetch<br>SLOT 0                              | Fetch<br>SLOT 1      | Fetch<br>SLOT 2      | Fetch<br>SLOT 3      | Fetch<br>SLOT 4 |    |

|         |                      |                      | Predict cy                                | cle                                          | Control cycle                                | Fetch                | cycle                |                      |                 |    |

| June 4, | 2005                 |                      |                                           | UT-Aust                                      | n TRIPS Tu                                   | torial               |                      |                      |                 | 79 |

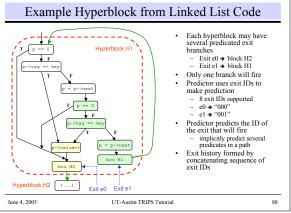

| <ul> <li>Dynamic block sequence</li> </ul>          | 111 III I                 | H H2 H1 H1 H1 H2       |

|-----------------------------------------------------|---------------------------|------------------------|

| 5 1                                                 |                           | 11 112 111 111 111 112 |

| <ul> <li>Local exit history for block H</li> </ul>  |                           |                        |

| <ul> <li>Local exit history encoding (2)</li> </ul> | /                         |                        |

| <ul> <li>Use only 2 bits from each 3-</li> </ul>    | bit exit to permit longer | histories              |

| <ul> <li>History table entry holds 5 ex</li> </ul>  | it IDs                    |                        |

| · Prediction table contains exit                    | IDs and hysteresis bi     | ts                     |

|                                                     | 5                         |                        |

| Exit history register                               | Prediction table entry    | Predictor action       |

|                                                     |                           |                        |

| 01 01 01 00 01 01 01 00                             | 001                       | Predict "001"          |

| 01 01 01 00 01 01 01 00                             | 000                       | Update history         |

|                                                     |                           |                        |

| 01 01 01 00 01 01 01 00                             | 000                       | Predict "000"          |

|                                                     | 001                       | Up date history        |

| 01 01 01 00 01 01 01 00                             | 001                       |                        |

| 01 01 01 00 01 01 01 00                             | 001                       |                        |

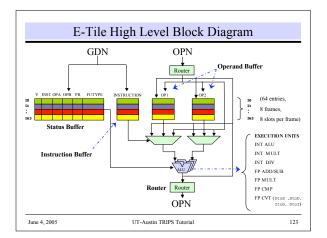

| Functional Unit    | Latency        | Implementation |

|--------------------|----------------|----------------|

| Integer ALU        | 1              | Synopsys IP    |

| Integer Multiplier | 3 (Pipelined)  | Synopsys IP    |

| Integer Divider    | 24 (Iterative) | Synopsys IP    |

| FP Add / Sub       | 4 (Pipelined)  | Synopsys IP    |

| FP Multiplier      | 4 (Pipelined)  | Synopsys IP    |

| FP Comparator      | 2 (Pipelined)  | Synopsys IP    |

| FP DtoI Convert    | 2 (Pipelined)  | Synopsys IP    |

| FP ItoD Convert    | 3 (Pipelined)  | Synopsys IP    |

| FP StoD Convert    | 2 (Pipelined)  | UT TRIPS IP    |

| FP DtoS Convert    | 3 (Pipelined)  | UT TRIPS IP    |

| TLB  | Dep. Pr       | LSQ  | Cache | Response                                                                         |

|------|---------------|------|-------|----------------------------------------------------------------------------------|

| Miss | -             |      | -     | Report TLB Exception                                                             |

| Hit  | Wait<br>(Hit) | -    | -     | Defer load until all prior stores are received. Non deterministic latency        |

| Hit  | Miss          | Miss | Hit   | Forward data from L1 Cache                                                       |

| Hit  | Miss          | Miss | Miss  | Forward data from L2 Cache (or memory<br>Issue cache fill request (if cacheable) |

| Hit  | Miss          | Hit  | Hit   | Forward data from LSQ                                                            |

| Hit  | Miss          | Hit  | Miss  | Forward data from LSQ<br>Issue cache fill request (if cacheable)                 |

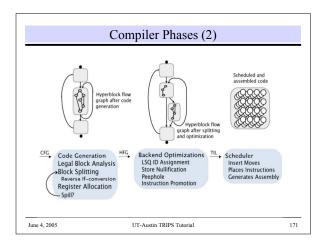

UT-Austin TRIPS Tutorial

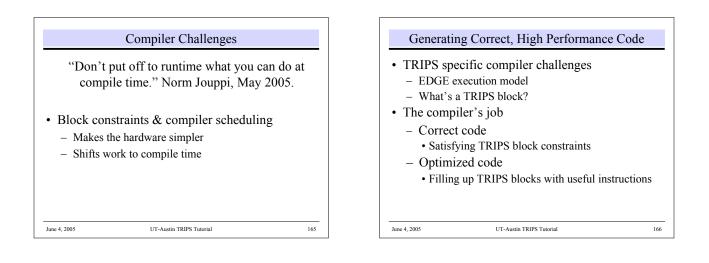

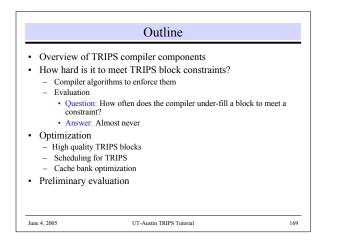

- Most corrections constraints

- Meet correctness constraints

June 4, 2005

173

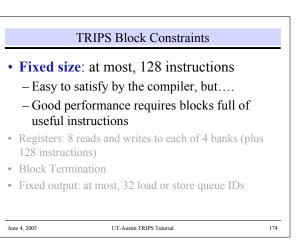

| min max mean min max mean |

|---------------------------|

| min max mean min max mean |

| SPEC2000 7 42 16 8 42 18  |

| EEMBC 7 31 16 9 67 22     |

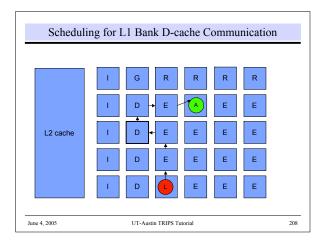

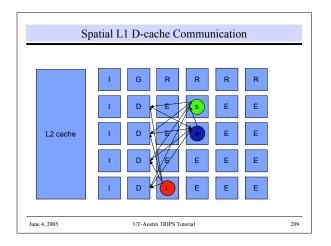

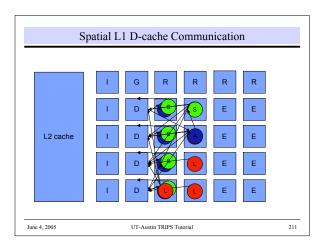

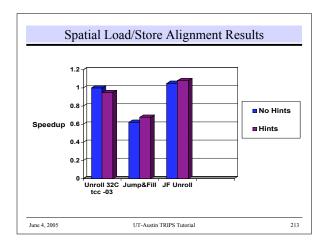

| • Pro | lem                                                   |  |

|-------|-------------------------------------------------------|--|

|       | oad/store mapping to data L1 cache                    |  |

|       | nk unknown to compiler                                |  |

| • Exa | nple                                                  |  |

|       | or (i=0; i<1024; i++) {                               |  |

| /     | A[i], L[i], B[i] to all banks<br>A[i] += L[i] + B[i]; |  |

| }     |                                                       |  |

|       |                                                       |  |

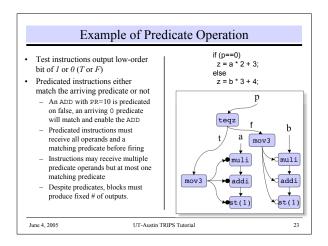

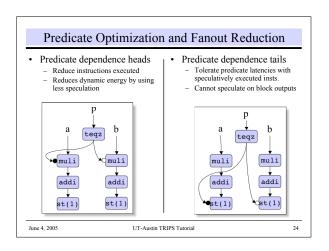

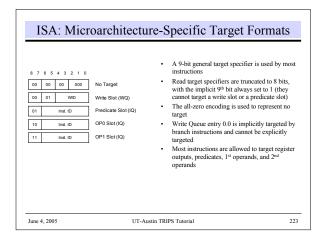

| PR | Description           | <ul> <li>Any instruction using the G, I, L, S, or B formation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 | Not Predicated        | may be predicated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 01 | (Reserved)            | <ul> <li>A 2-bit predicate field specified whether an<br/>instruction is not directed with the second secon</li></ul> |

| 10 | Predicated Upon False | instruction is predicated and, if so, upon what<br>condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11 | Predicated Upon True  | <ul> <li>Predicated instructions must receive all of their<br/>normal operands plus a matching predicate<br/>before they are allowed to execute</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |                       | <ul> <li>Instructions that meet these criteria are said to<br/>be <i>enabled</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |                       | <ul> <li>Instructions that don't meet these criteria are<br/>said to be <i>inhibited</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    |                       | <ul> <li>Inhibited instructions may cause other<br/>dependent instructions to be indirectly inhibite</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                       | <ul> <li>A block completes executing when all of its<br/>register and memory outputs are produced (it is<br/>not necessary for all of its instructions to<br/>execute)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                         | ISA: Load                                                                                                                                                                                                                           | is and | 510105                                                                  |               |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------|---------------|

| Mnemonic                                                                                                | Name                                                                                                                                                                                                                                | Format | Sources                                                                 | Targets       |

| LB                                                                                                      | Load Byte                                                                                                                                                                                                                           | L      | OP0, IMM                                                                | T0            |

| LBS                                                                                                     | Load Byte Signed                                                                                                                                                                                                                    | L      | OP0, IMM                                                                | TO            |

| LH                                                                                                      | Load Halfword                                                                                                                                                                                                                       | L      | OP0, IMM                                                                | Т0            |

| LH                                                                                                      | Load Halfword Signed                                                                                                                                                                                                                | L      | OP0, IMM                                                                | T0            |

| LW                                                                                                      | Load Word                                                                                                                                                                                                                           | L      | OP0, IMM                                                                | TO            |

| LWS                                                                                                     | Load Word Signed                                                                                                                                                                                                                    | L      | OP0, IMM                                                                | Т0            |

| LD                                                                                                      | Load Doubleword                                                                                                                                                                                                                     | L      | OP0, IMM                                                                | Т0            |

| SB                                                                                                      | Store Byte                                                                                                                                                                                                                          | S      | OP0, OP1, IMM                                                           | None          |

| SH                                                                                                      | Store Halfword                                                                                                                                                                                                                      | S      | OP0, OP1, IMM                                                           | None          |

| SW                                                                                                      | Store Word                                                                                                                                                                                                                          | S      | OP0, OP1, IMM                                                           | None          |

| SD                                                                                                      | Store Doubleword                                                                                                                                                                                                                    | S      | OP0, OP1, IMM                                                           | None          |

| <ul> <li>LBS: T0 =</li> <li>LH: T0 =</li> <li>LHS: T0 =</li> <li>LW: T0 =</li> <li>LWS: T0 =</li> </ul> | <pre>ZEXT( MEM_B(OP0 + SEXT(INM)] ) SEXT( MEM_B(OP0 + SEXT(INM)] ) ZEXT( MEM_H(OP0 + SEXT(INM)] ) SEXT( MEM_H(OP0 + SEXT(INM)] ) SEXT( MEM_W(OP0 + SEXT(INM)] ) SEXT( MEM_W(OP0 + SEXT(INM)] ) ZEXT( MEM_D(OP0 + SEXT(INM)] )</pre> | • SW:  | MEM_H[OPO + SEXT(IMM)<br>MEM_W[OPO + SEXT(IMM)<br>MEM_D[OPO + SEXT(IMM) | ] = OP1[31:0] |

| Mnemonic | Name                      | Format | Sources  | Targets |

|----------|---------------------------|--------|----------|---------|

| ADD      | Add                       | G      | OP0, OP1 | T0, T1  |

| ADDI     | Add Immediate             | I      | OP0, IMM | T0      |

| SUB      | Subtract                  | G      | OP0, OP1 | T0, T1  |

| SUBI     | Subtract Immediate        | I      | OP0, IMM | T0      |

| MUL      | Multiply                  | G      | OP0, OP1 | T0, T1  |

| MULI     | Multiply Immediate        | I      | OP0, IMM | T0      |

| DIVS     | Divide Signed             | G      | OP0, OP1 | T0, T1  |

| DIVSI    | Divide Signed Immediate   | Ι      | OP0, IMM | T0      |

| DIVU     | Divide Unsigned           | G      | OP0, OP1 | T0, T1  |

| DIVUI    | Divide Unsigned Immediate | I      | OP0, IMM | T0      |

| ND  |                       | Format | Sources  | Targets |

|-----|-----------------------|--------|----------|---------|

| ND  | Bitwise AND           | G      | OP0, OP1 | T0, T1  |

| NDI | Bitwise AND Immediate | I      | OP0, IMM | T0      |

| R   | Bitwise OR            | G      | OP0, OP1 | T0, T1  |

| RI  | Bitwise OR Immediate  | I      | OP0, IMM | T0      |

| OR  | Bitwise XOR           | G      | OP0, OP1 | T0, T1  |

| ORI | Bitwise XOR Immediate | I      | OP0, IMM | T0      |

|                                              | ISA: Int                                                                                                                          | leger 3                  | Shill    |               |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------|---------------|

| Mnemonic                                     | Name                                                                                                                              | Format                   | Sources  | Targets       |

| SLL                                          | Shift Left Logical                                                                                                                | G                        | OP0, OP1 | T0, T1        |

| SLLI                                         | Shift Left Logical Immediate                                                                                                      | I                        | OP0, IMM | T0            |

| SRL                                          | Shift Right Logical                                                                                                               | G                        | OP0, OP1 | T0, T1        |

| SRLI                                         | Shift Right Logical Immediate                                                                                                     | I                        | OP0, IMM | Т0            |

| SRA                                          | Shift Right Arithmetic                                                                                                            | G                        | OP0, OP1 | T0, T1        |

| SRAI                                         | Shift Right Arithmetic<br>Immediate                                                                                               | I                        | OP0, IMM | Т0            |

| <ul><li>Opera</li><li>The location</li></ul> | nd 1 provides the data to be<br>ind 2 or IMM provides the sh<br>ower 6 bits of the shift count<br>igher bits of the shift count a | nift count<br>are interp |          | gned quantity |

|                                              |                                                                                                                                   |                          |          |               |

| Mnemonic | Name                         | Format       | Sources        | Targets |

|----------|------------------------------|--------------|----------------|---------|

| EXTSB    | Extend Signed Byte           | G            | OP0            | T0, T1  |

| EXTSH    | Extend Signed Halfword       | G            | OP0            | T0, T1  |

| EXTSW    | Extend Signed Word           | G            | OP0            | T0, T1  |

| EXTUB    | Extend Unsigned Byte         | G            | OP0            | T0, T1  |

| EXTUH    | Extend Unsigned Halfword     | G            | OP0            | T0, T1  |

| EXTUW    | Extend Unsigned Word         | G            | OP0            | T0, T1  |

| • These  | are better than doing a left | shift follov | wed by a right | shift   |

| Mnemonic | Name             | Format | Sources  | Targets |

|----------|------------------|--------|----------|---------|

| TEQ      | Test EQ          | G      | OP0, OP1 | T0, T1  |

| INE      | Test NE          | G      | OP0, OP1 | T0, T1  |

| TLE      | Test LE          | G      | OP0, OP1 | T0, T1  |

| TLEU     | Test LE Unsigned | G      | OP0, OP1 | T0, T1  |

| TLT      | Test LT          | G      | OP0, OP1 | T0, T1  |

| TLTU     | Test LT Unsigned | G      | OP0, OP1 | T0, T1  |

| TGE      | Test GE          | G      | OP0, OP1 | T0, T1  |

| IGEU     | Test GE Unsigned | G      | OP0, OP1 | T0, T1  |

| TGT      | Test GT          | G      | OP0, OP1 | T0, T1  |

| TGTU     | Test GT Unsigned | G      | OP0, OP1 | T0, T1  |

| Mnemonic | Name                       | Format | Sources  | Targets |

|----------|----------------------------|--------|----------|---------|

| TEQI     | Test EQ Immediate          | I      | OP0, IMM | T1      |

| TNEI     | Test NE Immediate          | I      | OP0, IMM | Tl      |

| TLEI     | Test LE Immediate          | I      | OP0, IMM | T1      |

| TLEUI    | Test LE Unsigned Immediate | I      | OP0, IMM | T1      |

| TLTI     | Test LT Immediate          | I      | OP0, IMM | T1      |

| TLTUI    | Test LT Unsigned Immediate | I      | OP0, IMM | T1      |

| TGEI     | Test GE Immediate          | I      | OP0, IMM | T1      |

| TGEUI    | Test GE Unsigned Immediate | I      | OP0, IMM | T1      |

| TGTI     | Test GT Immediate          | I      | OP0, IMM | Tl      |

| TGTUI    | Test GT Unsigned Immediate | I      | OP0, IMM | Tl      |

|                           | Name                        | Format   | Sources         | Targets |

|---------------------------|-----------------------------|----------|-----------------|---------|

| FADD                      | FP Add                      | G        | OP0, OP1        | T0, T1  |

| FSUB                      | FP Substract                | G        | OP0, OP1        | T0, T1  |

| FMUL                      | FP Multiply                 | G        | OP0, OP1        | T0, T1  |

| FDIV                      | FP Divide (simulator only!) | G        | OP0, OP1        | T0, T1  |

| <ul> <li>These</li> </ul> | operations are performed as | suming d | ouble-precision | values  |

| Inemonic | Name       | Format | Sources  | Targets |

|----------|------------|--------|----------|---------|

| EQ       | FP Test EQ | G      | OP0, OP1 | T0, T1  |

| NE       | FP Test NE | G      | OP0, OP1 | T0, T1  |

| LE       | FP Test LE | G      | OP0, OP1 | T0, T1  |

| LT       | FP Test LT | G      | OP0, OP1 | T0, T1  |

| GE       | FP Test GE | G      | OP0, OP1 | T0, T1  |

| GT       | FP Test GT | G      | OP0, OP1 | T0, T1  |

UT-Austin TRIPS Tutorial

| Mnemonic                 | Name                           | Format   | Sources       | Targets   |

|--------------------------|--------------------------------|----------|---------------|-----------|

| FITOD                    | Convert Integer to Double FP   | G        | OP0           | T0, T1    |

| FDTOI                    | Convert Double FP to Integer   | G        | OP0           | T0, T1    |

| FSTOD                    | Convert Single FP to Double FP | G        | OP0           | T0, T1    |

| FDTOS                    | Convert Double FP to Single FP | G        | OP0           | T0, T1    |

| <ul> <li>FITO</li> </ul> | D: Converts a 64-bit signed in | teger to | a double-pree | sion moat |

June 4, 2005

| Mnemonic | Name               | Format | Sources | Targets |

|----------|--------------------|--------|---------|---------|

| BR       | Branch             | В      | OP0     | PC      |

| BRO      | Branch with Offset | В      | OFFSET  | PC +=   |

| CALL     | Call               | В      | OP0     | PC      |

| CALLO    | Call with Offset   | В      | OFFSET  | PC +=   |

| RET      | Return             | В      | OP0     | PC      |

| SCALL    | System Call        | В      | None    | PC      |

- Call and return behave like normal branches (but may be treated in a special way be a hardware branch predictor)

- The System Call instruction will trigger a System Call Exception

June 4, 2005 UT-Austin TRIPS Tutorial

235

| Mnemonic                                                           | Name                                                                                                                                                                                                                                                      | Format                 | Sources    | Targets        |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|----------------|

| NULL                                                               | Nullify Output                                                                                                                                                                                                                                            | G                      | None       | T0, T1         |

| MOV                                                                | Move                                                                                                                                                                                                                                                      | G                      | OP0        | T0, T1         |

| MOVI                                                               | Move Immediate                                                                                                                                                                                                                                            | I                      | IMM        | T0             |

| MOV3                                                               | Move to three targets                                                                                                                                                                                                                                     | M3                     | OP0        | T0, T1, T2     |

| MOV4                                                               | Move to four targets                                                                                                                                                                                                                                      | M4                     | OP0        | T0, T1, T2, T3 |

| MFPC                                                               | Move from PC                                                                                                                                                                                                                                              | I                      | None       | T0             |

| GENS                                                               | Generate Signed Constant                                                                                                                                                                                                                                  | C                      | CONST      | T0             |

| GENU                                                               | Generate Unsigned Constant                                                                                                                                                                                                                                | C                      | CONST      | T0             |

| APP                                                                | Append Constant                                                                                                                                                                                                                                           | C                      | OP0, CONST | T0             |

| NOP                                                                | No Operations                                                                                                                                                                                                                                             | C                      | None       | None           |

| Lock                                                               | Load and Lock                                                                                                                                                                                                                                             | L                      | OP0        | T0             |

| <ul> <li>MOV is t</li> <li>The gener</li> <li>Three ins</li> </ul> | a special instruction for cancelling one or more<br>the same as RPT (but with a conventional nam<br>rate and append instructions may be used to fo<br>tructions are required to form a 64-bit constant<br>ructions are required to form a 64-bit constant | e)<br>rm large constan | ts         |                |

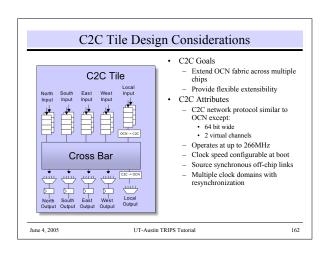

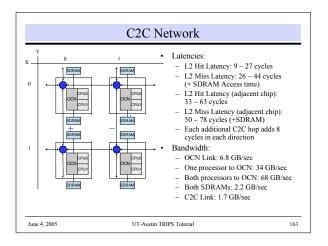

| Interface                               | Width    | Freq         | Multiplier | Bytes/Sec  |  |  |  |  |

|-----------------------------------------|----------|--------------|------------|------------|--|--|--|--|

| Processor Data Cache (Fill + Spill)     | 128 bits | 533 MHz      | 4*2        | 68 GB/s    |  |  |  |  |

| Processor Data Cache (Load + Store)     | 64 bits  | 533 MHz      | 4*2        | 34 GB/s    |  |  |  |  |

| Processor Inst Cache (Fetch or Fill)    | 128 bits | 533 MHz      | 4          | 34 GB/s    |  |  |  |  |

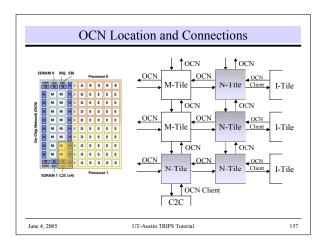

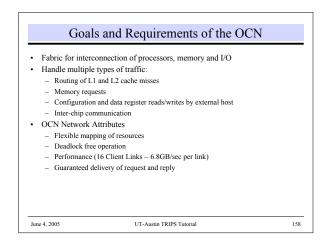

| Processor to OCN Interface              | 128 bits | 533 MHz      | 5*2*0.8    | 68 GB/s    |  |  |  |  |

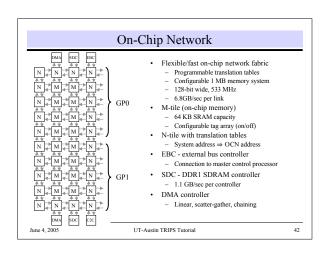

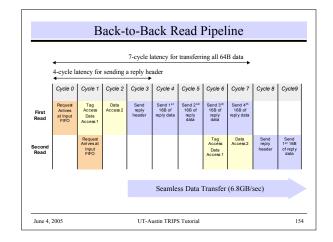

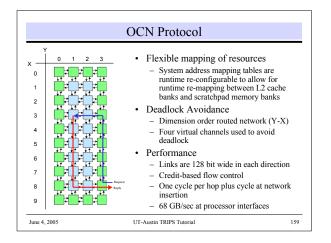

| On-Chip Network Link (64B Read)         | 128 bits | 533 MHz      | 0.8        | 6.8 GB/s   |  |  |  |  |

| On-Chip Memory Bank (64B Read)          | 128 bits | 533 MHz      | 0.8        | 6.8 GB/s   |  |  |  |  |

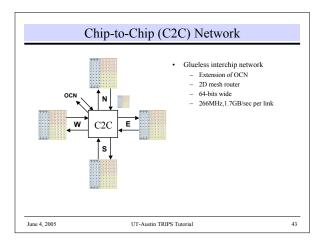

| Chip-to-Chip Network Link (64B<br>Read) | 64 bits  | (266<br>MHz) | 0.8        | (1.7 GB/s) |  |  |  |  |

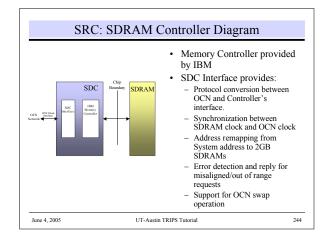

| DDR 266 SDRAM (64B Read)                | 64 bits  | 266 MHz      | 0.5        | 1.1 GB/s   |  |  |  |  |

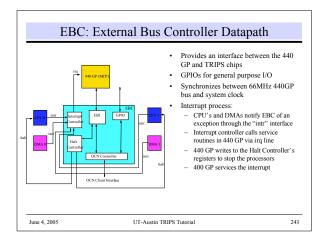

| External Bus Interface                  | 32 bits  | 66 MHz       | 0.33       | 88 MB/s    |  |  |  |  |