Copyright by Zhan Shi 2020 The Dissertation Committee for Zhan Shi certifies that this is the approved version of the following dissertation:

# Machine Learning for Prediction Problems in Computer Architecture

Committee:

Calvin Lin, Supervisor

Don Fussell

Qiang Liu

Milad Hashemi

# Machine Learning for Prediction Problems in Computer Architecture

by

Zhan Shi, B.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

## **DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2020

Dedicated to my mom and dad.

## Acknowledgments

My PhD experience has been a valuable journey for me, and for all that I have learned in the past years, I have many people to thank.

First and foremost, I am grateful to my advisor, Calvin Lin. It took around 2 weeks for me to realize that Dr. Lin is more of an educationist than a pure researcher or professor. Throughout my academic journey with Dr. Lin, I enjoy the respect and freedom that all my fellow students have been envying about. Dr. Lin patiently taught me the way to make impacts in the computer architecture community, and ensured that I learn from failures, and helped me see the bigger questions behind our research efforts. Also, I especially appreciate his thorough feedback on my presentation and writing, which has helped me organize my thoughts more logically and systematically.

I would also like to thank my committee members for their valuable feedback over the course of my PhD. Dr. Fussell has provided kind words of encouragement and important feedback on numerous occasions. Dr. Liu has given me very constructive comments on my RPE and proposal, and pointed out the directions that improved my work.

I have to give special thanks to my external committee member, Milad Hashemi. Milad has reshaped my Ph.D. through our 3-year collaboration, during which he has not only acted as my unofficial co-advisor, but also been a older brother who always gave me suggestions, shared his own experience, and shown me the way to do research and be a good person. I'm so lucky to have worked with Milad in my Ph.D..

I also need to thank Akanksha for being a role model. From her I know what a successfully student of Dr. Lin could be like, which is always motivating. I am thankful to my group members, Hao, Kai, Curtis, Jia, Molly, Chirag, Aparna, and Jack, my collaborators Kevin, Danny, Partha, and my colleagues at Google and Facebook, Ashish, Guangsha, Yuening, Ehsan and many others, for their support, feedback, and great company. Last but not the least, I am fortunate to have a great support system in my family and friends. My parents have supported me unconditionally throughout my graduate education. My girlfriend, Judy has provided tremendous encouragement and support. I will never forget the time when I realized that I needed to get my proposal done in 2 weeks, from writing, to a couple of practices, to the final talk. Judy believed more than I did that I could make it in time, and took the family responsibility during COVID without any complaints. Thank you for being my luck.

# Machine Learning for Prediction Problems in Computer Architecture

Publication No.

Zhan Shi, Ph.D. The University of Texas at Austin, 2020

Supervisor: Calvin Lin

The solutions to many problems in computer architecture involve predictions, which are often based on heuristics. Given the success of machine learning in solving prediction problems, it is natural to wonder if machine learning can better solve architectural prediction problems. Unfortunately, despite vastly outperforming traditional heuristics in various fields, machine learning has seen limited impact on prediction problems in computer architecture. The main challenge is that each architectural prediction problem exhibits unique constraints that prevent off-theshelf machine learning algorithms from being more effective than heuristics. For example, hardware prediction problems, such as branch prediction and cache replacement, impose severe latency and area constraints that make multi-layer neural networks largely infeasible.

In this thesis, we propose machine learning solutions to three important problems in computer architecture, namely cache replacement, data prefetching, and the automatic design of neural network accelerators. In our solutions, we focus on not only the design of learning algorithms, but also the use of learning algorithms under the unique constraints of each problem. In particular, to deal with the extremely tight area and latency constraints of replacement policies and data prefetchers, we propose to first design powerful yet impractical neural network models, from which we derive important insights that can be used to design practical predictors. To deal with the highly constrained search space in the automated design of neural network accelerators, we propose a new constrained Bayesian optimization framework to effectively explore the search space where over 90% of designs are infeasible.

# **Table of Contents**

| 0     |                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ct    |                                                                                                                                                                                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table | s                                                                                                                                                                               | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figur | es                                                                                                                                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| er 1. | Introduction                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| er 2. | Related Work                                                                                                                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Cach  | ne Replacement                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Data  | Prefetching                                                                                                                                                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Neu   | al Network Accelerator                                                                                                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| er 3. | Glider Cache Replacement Policy                                                                                                                                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Back  | ground and Constraints                                                                                                                                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1.1 | The Hawkeye Cache                                                                                                                                                               | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1.2 | Recurrent Neural Networks                                                                                                                                                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1.3 | Attention Mechanisms                                                                                                                                                            | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1.4 | Hardware Constraints on the Predictor                                                                                                                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Our   | Solution                                                                                                                                                                        | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.1 | LSTM with Scaled Attention                                                                                                                                                      | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.2 | 2 Insights from Our LSTM Model                                                                                                                                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.3 | Integer SVM and a k-sparse Binary Feature                                                                                                                                       | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.4 | Hardware Design                                                                                                                                                                 | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Eval  | uation                                                                                                                                                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.1 | Methodology                                                                                                                                                                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3.2 | Comparison of Offline Models                                                                                                                                                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | ct<br>Table<br>Figur<br>er 1.<br>er 2.<br>Cach<br>Data<br>Neun<br>er 3.<br>Back<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Our<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Eval<br>3.3.1 | Tables         Figures         er 1. Introduction         er 2. Related Work         Cache Replacement         Data Prefetching         Data Prefetching         Neural Network Accelerator         Neural Network Accelerator         er 3. Glider Cache Replacement Policy         Background and Constraints         3.1.1 The Hawkeye Cache         3.1.2 Recurrent Neural Networks         3.1.3 Attention Mechanisms         3.1.4 Hardware Constraints on the Predictor         Our Solution         3.2.1 LSTM with Scaled Attention         3.2.2 Insights from Our LSTM Model         3.2.3 Integer SVM and a k-sparse Binary Feature         3.2.4 Hardware Design |

|        | 3.3.3 Comparison of Online Models                            | 35          |

|--------|--------------------------------------------------------------|-------------|

|        | 3.3.4 Practicality of Glider vs. LSTM                        | 39          |

|        | 3.3.5 Learning High-Level Program Semantics                  | 42          |

|        | 3.3.6 Model Specifications                                   | 45          |

| 3.4    | Summary                                                      | 45          |

| Chapte | er 4. Voyager Data Prefetcher                                | 47          |

| 4.1    | Challenges of Data Prefetching as a Machine Learning Problem | 47          |

| 4.2    | Problem Formulation                                          | 48          |

|        | 4.2.1 Probabilistic Formulation of Prefetching               | 48          |

| 4.3    | Our Solution: Voyager                                        | 50          |

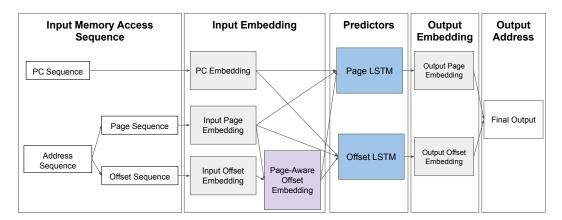

|        | 4.3.1 Model Overview                                         | 51          |

|        | 4.3.2 Hierarchical Neural Structure                          | 51          |

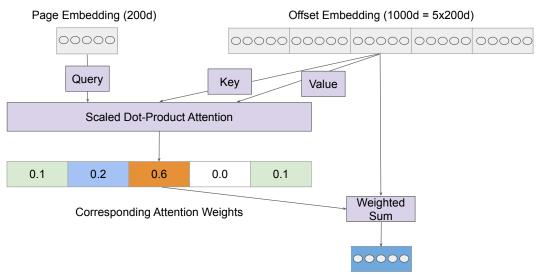

|        | 4.3.3 Page-Aware Offset Embedding Mechanism                  | 54          |

|        | 4.3.4 Multi-Label Training Scheme                            | 56          |

| 4.4    | Evaluation                                                   | 57          |

|        | 4.4.1 Methodology                                            | 57          |

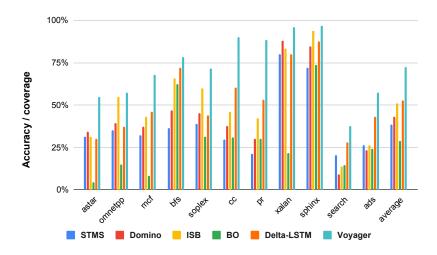

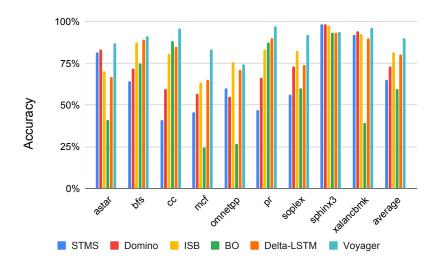

|        | 4.4.2 Comparison With Prior Art                              | 60          |

|        | 4.4.3 Understanding Voyager's Benefits                       | 62          |

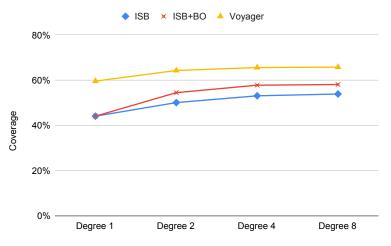

|        | 4.4.3.1 Prefetch with High Degree                            | 62          |

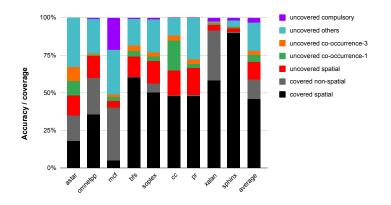

|        | 4.4.3.2 Access Patterns Breakdown                            | 63          |

|        | 4.4.3.3 Features and Labels                                  | 65          |

|        | 4.4.4 Why ML-Based Prefetchers                               | 68          |

|        | 4.4.5 Model Compression and Overhead                         | 70          |

|        | 4.4.6 Model Specifications                                   | 72          |

|        | 4.4.7 Paths to Practicality                                  | 72          |

| 4.5    | Summary                                                      | 74          |

| Chapte |                                                              | esian<br>76 |

| 5.1    | A Formal Representation of Software and Hardware             | 76          |

|        | 5.1.1 Parameterizing the Design Space                        | 76          |

|        | 5.1.2 Constraints in the Design Space                        | 79          |

| 5.2     | Bayes | ian Optimization                                  | . 79 |

|---------|-------|---------------------------------------------------|------|

|         | 5.2.1 | Overview                                          | . 79 |

|         | 5.2.2 | Gaussian processes                                | . 80 |

|         | 5.2.3 | Acquisition functions                             | . 81 |

|         | 5.2.4 | Constraints                                       | . 82 |

| 5.3     | Bayes | ian Optimization for Hardware/Software Co-design  | . 84 |

|         | 5.3.1 | Overview of Nested Hardware/Software Optimization | . 84 |

|         | 5.3.2 | BO for Optimizing Hardware Architectures          | . 87 |

|         | 5.3.3 | BO for Optimizing Software Mappings               | . 88 |

| 5.4     | Evalu | ation                                             | . 89 |

|         | 5.4.1 | Methodology                                       | . 89 |

|         | 5.4.2 | Software Mapping Optimization                     | . 94 |

|         | 5.4.3 | Hardware Configuration Optimization               | . 95 |

|         | 5.4.4 | Ablations                                         | . 96 |

| 5.5     | Summ  | nary                                              | . 97 |

| Chapte  | r6. ( | Conclusions                                       | 98   |

| Bibliog | raphy |                                                   | 100  |

| Vita    |       |                                                   | 122  |

# List of Tables

| 3.1 | Statistics for benchmarks used in offline analysis                                                                                                        |    |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 3.2 | Baseline configuration.                                                                                                                                   | 31 |  |  |  |

| 3.3 | Statistics for benchmarks used in offline analysis                                                                                                        | 32 |  |  |  |

| 3.4 | Model size and computation cost. LSTM uses floating point opera-<br>tions; the other models use integer ops                                               | 39 |  |  |  |

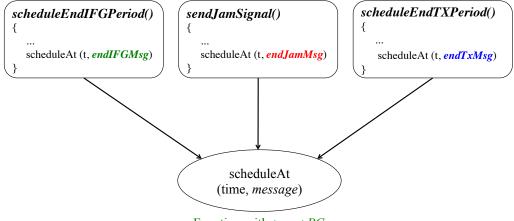

| 3.5 | The attention-based LSTM model improves accuracy for four target PCs in <i>scheduleAt()</i> method, and all four target PCs attend to the same source PC. | 42 |  |  |  |

| 3.6 | Offline Model Specifications                                                                                                                              | 45 |  |  |  |

| 4.1 | Benchmark statistics.                                                                                                                                     | 52 |  |  |  |

| 4.2 | Simulation configuration.                                                                                                                                 | 58 |  |  |  |

| 4.3 | Hyperparameters for training Voyager.                                                                                                                     | 73 |  |  |  |

# List of Figures

| 3.1  | Overview of the Hawkeye Cache                                                                                                                                                                                                                                                                                              | 14 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Improvements in predictor accuracy lead to increased speedup                                                                                                                                                                                                                                                               | 17 |

| 3.3  | Our LSTM-based sequence labeling model takes as input a sequence<br>of PCs and produces as output cache-friendly (1) or cache-averse<br>(0) labels.                                                                                                                                                                        | 19 |

| 3.4  | The attention-based LSTM network architecture. LSTM handles a sequence of input recurrently                                                                                                                                                                                                                                | 20 |

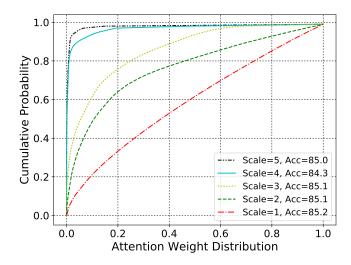

| 3.5  | Cumulative distribution function of attention weight distribution for omnetpp.                                                                                                                                                                                                                                             | 23 |

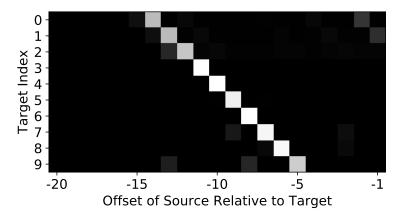

| 3.6  | Attention weight vectors of consecutive memory accesses. The y-<br>axis shows the indices of target memory accesses, and the x-axis<br>shows the offset of source memory accesses from the target. The<br>white boxes show that target memory accesses are strongly corre-<br>lated with just a few source memory accesses | 24 |

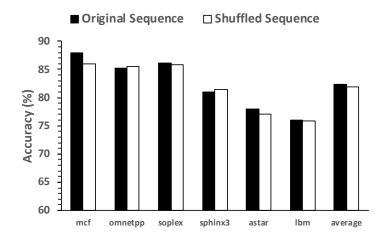

| 3.7  | Accuracy for the original ordered sequence and the randomly shuf-<br>fled sequence.                                                                                                                                                                                                                                        | 25 |

| 3.8  | Examples of $k$ -sparse binary feature. For simplicity, the total number of PCs is 4 and $k$ is 3                                                                                                                                                                                                                          | 26 |

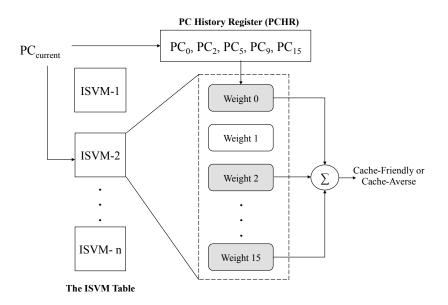

| 3.9  | The Glider predictor.                                                                                                                                                                                                                                                                                                      | 29 |

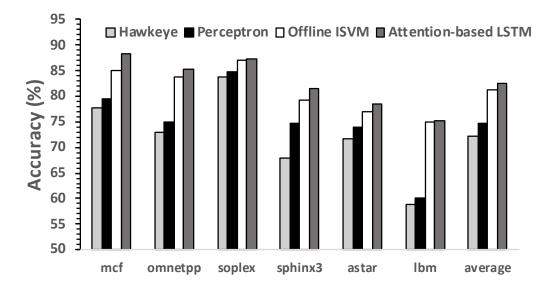

| 3.10 | Accuracy comparison of offline predictors                                                                                                                                                                                                                                                                                  | 35 |

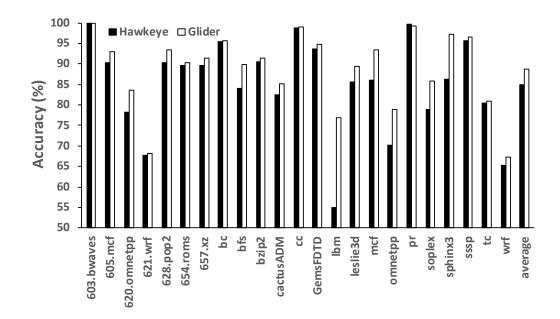

| 3.11 | Accuracy comparison of online predictors                                                                                                                                                                                                                                                                                   | 36 |

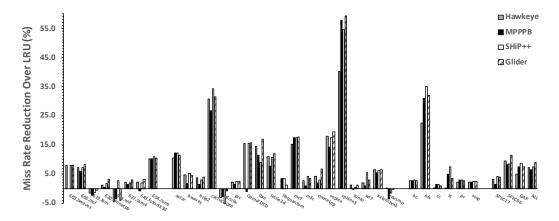

| 3.12 | Miss rate reduction for single-core benchmarks                                                                                                                                                                                                                                                                             | 36 |

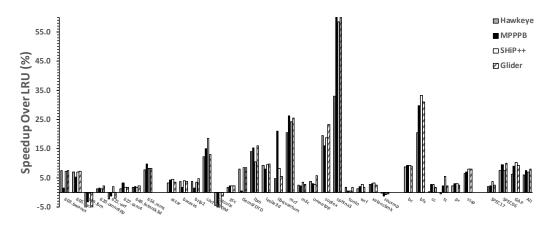

| 3.13 | Speedup comparison for single-core benchmarks                                                                                                                                                                                                                                                                              | 37 |

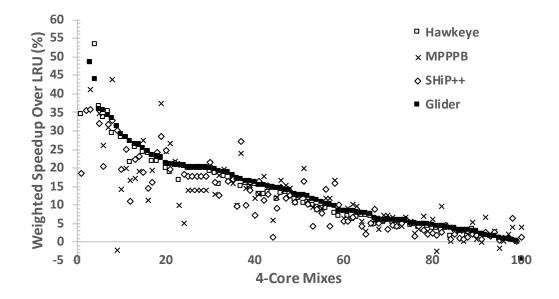

| 3.14 | Weighted speedup for 4 cores with a shared 8MB LLC                                                                                                                                                                                                                                                                         | 38 |

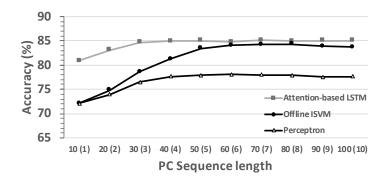

| 3.15 | Sequence length for attention-based LSTM (number of unique PCs for offline ISVM and sequence length for Perceptron)                                                                                                                                                                                                        | 39 |

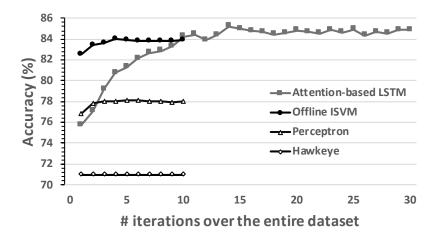

| 3.16 | Convergence of different models                                                                                                                                                                                                                                                                                            | 41 |

| 3.17 | The anchor PC belongs to one of the calling contexts for the target PCs.                                                                                                                                                                                                                                                   | 43 |

| 3.18 | Source code and assembly code for target PC 44c7f6 in <i>scheduleAt()</i> method (lines in bold).                                                                                                                                                                                                                          | 44 |

| 4.1  | Overview of Voyager                                                                                                                             |    |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| 4.2  | Page-aware offset embedding with the dot-product attention mech-<br>anism.                                                                      | 53 |  |  |

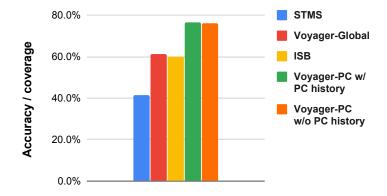

| 4.3  | Unified accuracy/coverage, including Google's Search and Ads                                                                                    | 60 |  |  |

| 4.4  | Accuracy                                                                                                                                        | 61 |  |  |

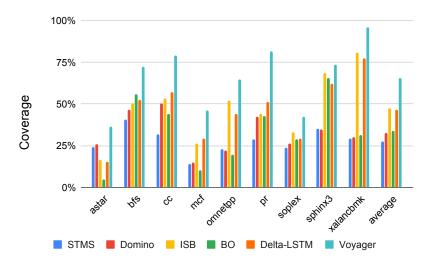

| 4.5  | Coverage                                                                                                                                        | 62 |  |  |

| 4.6  | IPC                                                                                                                                             | 63 |  |  |

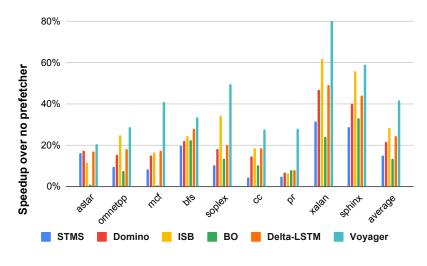

| 4.7  | Sensitivity to Prefetch degree.                                                                                                                 | 64 |  |  |

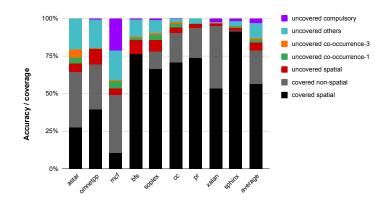

| 4.8  | Breakdown of the patterns of ISB                                                                                                                | 65 |  |  |

| 4.9  | Breakdown of the patterns of Voyager w/o delta                                                                                                  | 65 |  |  |

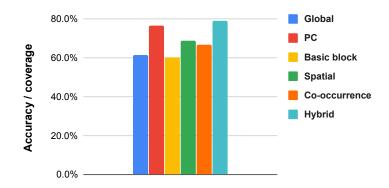

| 4.10 | Comparison of different features                                                                                                                | 67 |  |  |

| 4.11 | Comparison of different labeling schemes                                                                                                        | 67 |  |  |

| 4.12 | Code example from PageRank                                                                                                                      | 69 |  |  |

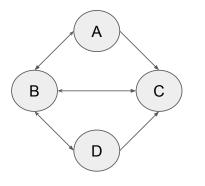

| 4.13 | An example input graph to PageRank.                                                                                                             | 70 |  |  |

| 4.14 | Code example from Soplex                                                                                                                        | 71 |  |  |

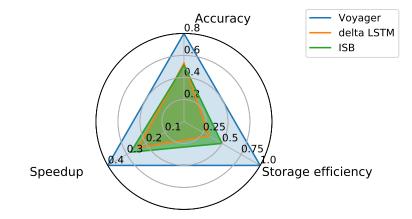

| 4.15 | Voyager wins on accuracy, speedup, and storage efficiency. Here storage efficiency is log-scaled and defined as $\frac{1}{1+log_{10}(storage)}$ | 72 |  |  |

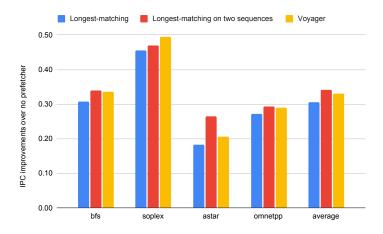

| 4.16 | Longest matching on a single sequence and two sequences (global and PC-localized) approximate Voyager.                                          | 74 |  |  |

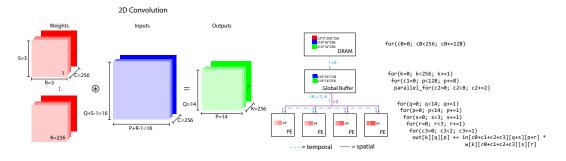

| 5.1  | Computing a 2D convolution with a seven-level nested loop                                                                                       | 77 |  |  |

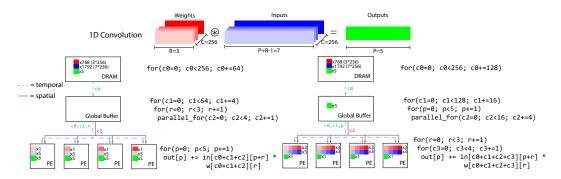

| 5.2  | Two architectures computing a 1D convolution.                                                                                                   | 78 |  |  |

| 5.3  | An architecture computing the CONV4 layer of ResNet                                                                                             | 78 |  |  |

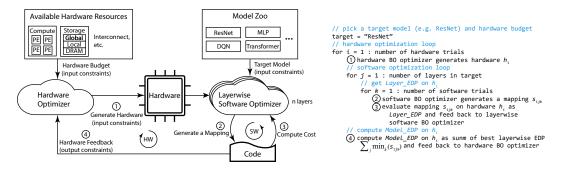

| 5.4  | Overview of BO-based nested search for hardware/software co-                                                                                    |    |  |  |

|      | design                                                                                                                                          | 85 |  |  |

| 5.5  | Hyperparamters for BO.                                                                                                                          | 86 |  |  |

| 5.6  | Hardware parameters                                                                                                                             | 88 |  |  |

| 5.7  | Hardware constraints                                                                                                                            | 89 |  |  |

| 5.8  | Extra features used by the hardware and software BO optimizers                                                                                  | 89 |  |  |

| 5.9  | Software parameters                                                                                                                             | 90 |  |  |

| 5.10 | Software constraints                                                                                                                            | 91 |  |  |

| 5.11 | Specifications of ResNet (ResNet-18) [34] and DQN [85]                                                                                          | 92 |  |  |

| 5.12 | Specifications of MLP and Transformer [123]                                                                                                     | 93 |  |  |

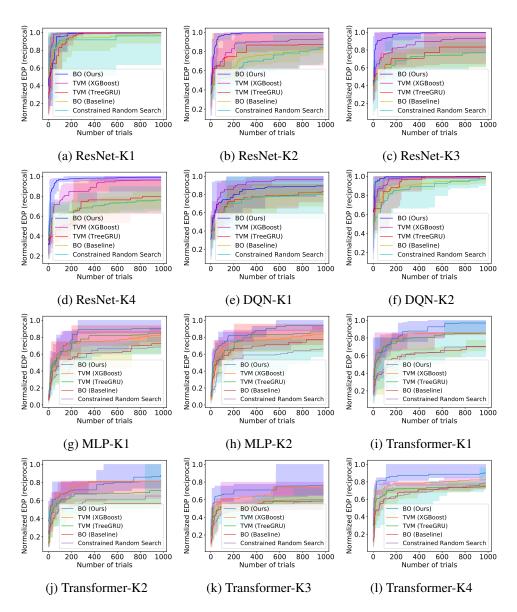

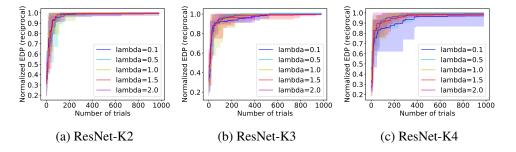

| 5.13 | Software mapping optimization on ResNet, DQN, MLP, and Transformer. The Y-axis shows the reciprocal of energy-delay product (EDP) (normalized against the best EDP value). Higher is better                                                            | 94 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

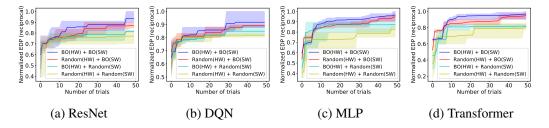

| 5.14 | Hardware/software co-optimization. The x-axis shows the number<br>of trials for hardware search, and 250 attempts are made to find<br>the optimal software mapping for each layer in the model on the<br>hardware specification. Best viewed in color. | 95 |

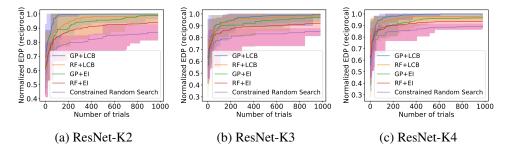

| 5.15 | GP with different surrogate models and acquisition functions                                                                                                                                                                                           | 96 |

| 5.16 | LCB acquisition function with different lambda values                                                                                                                                                                                                  | 96 |

|      |                                                                                                                                                                                                                                                        |    |

# Chapter 1

## Introduction

Machine learning has exploded in popularity for its ability to achieve stateof-the-art performance in a multitude of applications [75, 40, 85, 72]. These learning algorithms are capable of outperforming heuristic-driven approaches by extracting useful features in a data-driven fashion. Ideally, machine learning would be a powerful tool for computer architecture research, because heuristic-based predictions are commonly used in predictive mechanisms in speculative execution. For example, branch predictors [58, 103] predict a binary output—Taken or Not Taken—and cache replacement can be framed as a binary prediction—a line has either high or low priority for eviction [131, 52, 121]. Unfortunately, except for a few successes [58, 47, 59], machine learning has still not been widely adopted in hardware predictors [93].

The main challenges of applying machine learning are the unique constraints of each hardware prediction problem. For example, hardware cache replacement policies need to adapt to dynamic changes in the workload, so predictors for cache replacement are trained dynamically as the program executes. By contrast, deep learning models make multiple iterations over the training data and can take weeks or months to train. Moreover, the typical size of a hardware predictor for cache replacement is tens of bytes and a prediction must be produced in 20-30 CPU cycles (5-7 ns for a 4 GHz processor) [107, 1]. By contrast, deep learning models typically take megabytes to gigabytes of storage and microseconds to milliseconds to make a prediction.

Recent work shows the challenges of directly applying off-the-shelf machine learning to other architectural problems. For example, Tarsa et al. [120] and Zangeneh et al. [81] apply convolutional neural networks (CNNs) [72, 34] to branch prediction, which is another prediction mechanism that faces the tight area and latency constraints similar to cache replacement [57]. As shown in both papers [120, 81], although CNNs are capable of achieving superior accuracy, the models are too expensive to be deployed on chip. In particular, although a CNN with a unlimited budget shows the headroom of 2.9% IPC improvements over the state-of-theart [103], the number shrinks to 0.6% when it comes to a practical CNN that fits on a chip area [81].

Similar issues apply to other hardware predictors, such as data prefetchers. In data prefetching, the predictor is not only constrained by tight latency, but also needs to learn correlations among tens of millions of unique address values. As a result, the large number of data addresses limits the accuracy of neural networks, which are designed for traditional tasks with orders of magnitude fewer unique values, such as natural language.

Beyond hardware predictors, machine learning could potentially be a powerful tool in the area of design automation of domain-specific accelerators. Design automation of neural accelerator relies on a cost model to predict the performance and energy efficiency of possible designs, and the accuracy of the cost model determines the efficiency and effectiveness of the exploration process. However, due to constraints such as hardware budget, over 90% of hardware and software designs are invalid. As a result, the sparse and irregular search space leads to an inaccurate cost model that can severely hurt the efficiency of design space exploration.

The goal of this thesis is to find practical ways to use machine learning for hardware architecture problems under unique constraints and challenges. In particular, we first understand the root causes that prevent the effective use of machine learning techniques, and then we propose novel uses of machine learning that are specifically designed for each unique problem.

In the first part of this thesis, we focus on the extensively-studied problem of cache replacement. Cache replacement policies have evolved from ever more sophisticated heuristic-based solutions [102, 55, 118, 96, 3, 119, 22, 23] to learning-based solutions [130, 132, 52, 53, 121, 59]. We continue this trend by designing a powerful LSTM [41] learning model that can in an offline setting provide better accuracy than the state-of-the-art hardware predictors [52]. However, the offline LSTM exceeds the storage and latency requirements by 3 orders of magnitude. As the offline deep learning models is still not ready for direct use as hardware predictors, we need to understand why the offline LSTM provides accuracy improvements. To achieve this, we perform analysis to interpret this LSTM model with the scaled attention mechanism [80, 123], deriving a key insight that allows us to design a simple online model that matches the offline model's accuracy with orders of magnitude lower cost [107].

In the second part of this thesis, we focus on data prefetching, which is another extensively-studied memory optimization technique. Unlike previous neural models for prefetching that were limited to learning delta correlations [33, 117], we propose Voyager that can also learn address correlations, which are more powerful [50, 134, 133, 126, 5]. The major challenge of learning address correlations is that the number of data addresses are orders of magnitude larger than the number of unique categories in traditional machine learning tasks, such as natural language [80, 123]. The explosion of addresses not only leads to a significant increase in memory usage that could fail the training of neural networks, but also results in an ineffective representation of memory address space as each address only appears a few times, which is insufficient for training neural networks [33]. To solve this problem, we propose a hierarchical structure that separates addresses into pages and offsets [108]. The core of the hierarchical structure is a novel attention-based embedding mechanism for learning important relations among pages and offsets, and having pages provides contextual information for offsets. Though highly accurate, Voyager is still too expensive in computation to be practical for direct use in hardware. Therefore, we found two important insights that can lead to a practical prefetcher. First, the coverage of Voyager can be approximated with longest matching on two sequences of memory accesses, namely global sequence and PC localized sequence. Second, the order information is no longer important after we extract the longest-matched patterns, which helps us reduce the storage overhead by 33.6%.

In the third part of this thesis, we shift our focus from predictions problems

in hardware to the design of specialized deep learning accelerators. The compute and energy requirements of deep learning are growing [38], giving rise to numerous specialized hardware and software systems for deep learning. However, the design of such a system is typically driven by manual heuristics [17, 16, 21], or more recently heuristic-based search [135]. Therefore, we propose to cast the problem as hardware/software co-design, with the goal of automatically identifying desirable points in the joint design space [109]. The main challenge is that the highly constrained design space is semi-continuous / semi-discrete, meaning that a parameter can only take on a few discrete values, but their absolute values of the parameter affects the objective. The key to our solution is a new constrained Bayesian optimization framework that avoids invalid solutions through input and output constraints.

**Thesis Statement.** Machine learning can be a powerful tool in the solution of prediction problems in computer architecture, but to be effective, we need to devise new methods of tailoring machine learning techniques to these specific problems.

This thesis will make the following contributions:

1. We use cache replacement as a case study to explore the use of deep learning in hardware predictors that need to be dynamically trained and extremely efficient. Our solution is a three-step approach. In particular, we first build an offline deep learning model that achieves superior accuracy. In the second step, we derive the insights from the deep learning model that explains the advantage of deep learning models. In the last step, we use the insights to design the practical and effective Glider cache replacement policy that improves the miss rate reduction over LRU from 7.1% to 8.9% in a single-core setting, and on a four-core system, improves IPC over LRU from 13.6% to 14.7%.

- 2. We apply our three-step approach to data prefetching, which is more challenging in all three steps. We first build a hierarchical offline deep learning model that can handle a vast memory address space. In particular, we build our domain knowledge into the neural model that separates addresses into pages and offsets, and we introduce a mechanism for learning important relations among pages and offsets. The proposed hierarchical neural model, which we refer to as Voyager, achieves an average IPC improvement of 41.6% over a system with no prefetcher, compared with 28.2% of prior art. At present, slow training and prediction still preclude Voyager from being practical in hardware. Therefore, in the second step, we derive insights of prefetching patterns, based on which comparable prefetching coverage can be approximated using tables without neural networks. We leave for future work to finish the third step for a practical design, which requires a smart management of tables.

- 3. For the automatic design of deep learning accelerators, we introduce a constrained Bayesian optimization framework that effectively handles the constrained feature space in which over 90% of design points are invalid. Our constrained Bayesian optimization framework is significantly faster and more robust than the constrained random search algorithm. As a result, our framework improves the energy-delay product (EDP) over the state-of-the-art ac-

celerator by 18.3% on ResNet, 40.2% on DQN, 21.8% on MLP, and 16.0% on Transformer.

This thesis is organized as follows. Section 2 places our work in the context of prior work. A detailed discussion and evaluation of the Glider replacement policy is presented in Section 3. Section 4 discusses the Voyager data prefetcher, and we introduce the constrained Bayesian optimization framework in Section 5. Finally, Section 6 concludes the dissertation.

# Chapter 2

## **Related Work**

We now place our work in the context of the considerable prior work of cache replacement, data prefetching and accelerator design respectively.

## 2.1 Cache Replacement

Replacement policies have evolved from heavily heuristic-based solutions to learning-based solutions. However, despite of its success in various fields, deep learning has not been used for hardware cache replacement.

**Heuristic-Based Solutions.** Most prior cache replacement policies uses heuristics to exploit commonly observed access patterns. The majority of prior work build on LRU, MRU and combinations of the two [111, 129, 76, 66, 27, 95, 102, 55, 118, 96, 42, 3, 119, 22, 23, 78, 68]. The rest of heuristic are based on frequency counters [99, 30, 69], re-reference interval prediction [55]. and the reuse distance [42, 3, 119, 22, 23]. A common downside of all heuristic-based policies is that they rely on human intuition to customize for a limited class of known cache access patterns.

**Learning-Based Solutions.** Recent advancement [67, 131, 52, 53] takes a learningbased approach that leverages the past caching behavior to predict future caching priorities. However, there has been almost no prior work that applies machine learning to the cache replacement problem. One notable exception [121] uses an online perceptron [100] to improve the accuracy of cache replacement predictors, but this solution sees only marginal improvements because it uses naive feature representations that result in a limited program context. More recently, Teran et al.'s perceptron was outperformed by MPPPB [60], which uses offline genetic algorithms to choose relevant features from a comprehensive list of hand-crafted features that go beyond control-flow information. Our work differs from MPPPB by identifying insights that lead to a more effective feature representation.

## 2.2 Data Prefetching

Prior work in data prefetching can also be described as either heuristicbased or learning-based. The vast majority of prefetchers are heuristic-based, meaning that they predict future memory accesses based on pre-determined patterns. Learning-based approaches, however, learn rules from the past access patterns and apply to the future execution.

Heurstic-Based Solutions. Many regular prefetchers predict sequential [112, 64, 44] or strided [89, 4, 25, 48, 101] streams by detecting constant strides in sequences of memory accesses. For example, stream buffers [64, 89, 4] confirm a constant stride if k consecutive memory accesses are the same stride apart. *Offset*-

*based* prefetchers [94, 82] improve upon these ideas by testing a few pre-determined strides to select an offset that provides the best coverage. Instead of predicting constant offsets, another class of prefetchers uses *delta correlation* to predict recurring delta patterns [88, 106]. Some irregular accesses can be captured by predicting recurring spatial patterns across different regions in memory [61, 73, 13, 14, 115]. For example, the SMS prefetcher [115] learns recurring spatial footprints within page-sized regions and applies old spatial patterns to new unseen regions, and the Bingo prefetcher [6] uses longer address contexts to predict footprints.

Temporal prefetchers learn irregular memory accesses by memorizing pairs of correlated addresses [19, 125]. Early temporal prefetchers correlated consecutive memory accesses in the global access stream [63, 87, 20, 114, 43, 127]. More recent temporal prefetchers look for correlations of consecutive addresses in a PClocalized stream [51, 134, 133]. This scheme improves coverage and accuracy due to the superior predictability of the PC-localized stream. Instead of using localization, Domino improve the predictability of temporal prefetchers by using two past addresses as contextual information [5].

A common limitation of all heuristic-based prefetchers is their use of simple known rules to identify the sequence of accesses, which limits the scope of patterns that can be detected. Recent work has also focused on improving the accuracy of aggressive stride prefetchers [10, 9].

**Learning-Based Solutions.** We now introduce previous learning-based prefetchers. Peled et al., use reinforcement learning to explore the correlation between pro-

gram contexts and memory addresses [92]. Their solution uses tables to learn a combinatorial number of context-address pairs, which leads to large storage overheads and slow training, and it precludes the learning of context-address pairs that do not repeat often. More recent solutions have instead used self-supervised learning to predict deltas, since it is easy to reduce the number of deltas to be smaller than than the number of addresses. For example, Hashemi et al. formulate delta prefetching as a classification problem and leverage LSTM neural networks [41] to find rich delta patterns [33, 110]. Recent work improves the efficiency of delta-based LSTM by compressing the input and output [117], but such work an undesirable tradeoff between coverage and efficiency.

#### 2.3 Neural Network Accelerator

Different from the use of traditional CPUs, the design of hardware accelerators is often accompanied by a customized software optimizer that determines the use of software optimizations, such as look blocking and reordering. We now describe prior work in the hardware and software optimizations for DNNs.

Hardware Accelerators for DNNs. Prior work has designed specialized hardware to execute neural networks. From the design point of view, nearly all hardware accelerators are manually designed. Google's TPU [65] uses systolic arrays [74], and NVIDIA's GPUs have tensor cores [2]. Specialized for convolutional neural networks (CNNs), Eyeriss [17] introduces a specific dataflow that exploits a reuse pattern exhibited by 2D convolutions. To improve scalability, Eyeriss v2 [18] uses a more sophisticated interconnect than its predecessor, and it also supports sparse CNNs. Prior work [91, 137] has dealt with sparsity by suppressing zero-valued activations and storing and operating on compressed data. Many other domain specific architectures have been proposed to take advantage of local communication patterns [24], 3D-stacked bandwidth memory [70, 28], or multi-chip modules [105].

Recent work [135] recognizes that the design space of specialized hardware is vast and proposes heuristics that can be leveraged to automatically synthesize hardware using a domain-specific language, Halide.

**Software Optimization for DNNs.** There has been considerable work on software optimizations for neural networks [128, 86, 11], which include optimizations, such as loop blocking (tiling), loop reordering, and loop unrolling, that affect the utilization of compute and storage resources. This optimization process has been recognized as a search problem, and compilers such as TVM [15] have used learned cost models to optimize execution efficiency. Similarly, Timeloop uses a grid or random search to optimize software mappings on a user-specified hardware architecture [90].

# **Chapter 3**

## **Glider Cache Replacement Policy**

### 3.1 Background and Constraints

Since our solution uses recurrent neural networks (RNNs) and attention mechanisms, we first provide background on hardware caches and these machine learning topics.

#### 3.1.1 The Hawkeye Cache

This work builds on the Hawkeye cache replacement policy [52], which casts cache replacement as a supervised learning problem in which a predictor is trained from the optimal caching solution for past cache accesses.

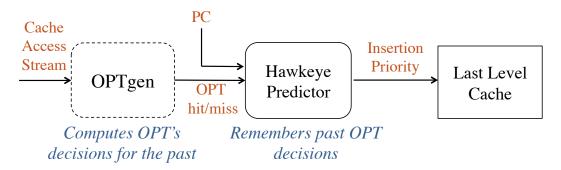

Figure 3.1 shows the overall structure of Hawkeye. Its main components are OPTgen, which simulates the optimal solution's behavior to produce training labels, and the Hawkeye Predictor which learns the optimal solution. The Hawkeye predictor is a binary classifier, whose goal is to predict whether a line loaded by a memory access is likely to be cached or not by the optimal algorithm. *Cache-friendly* data is inserted in the cache with high priority, and *cache-averse* data is inserted with low priority.

Hawkeye uses the program counter (PC) as a feature and maintains a table

Figure 3.1: Overview of the Hawkeye Cache.

of counters to learn whether memory accesses by a given PC tend to be cachefriendly or cache-averse. While the Hawkeye Cache has been quite successful—it won the 2017 Cache Replacement Championship [1]—its simple predictor achieves only 72.4% accuracy on a set of challenging benchmarks.

#### 3.1.2 **Recurrent Neural Networks**

Recurrent neural networks (RNNs) are extremely popular because they achieve state-of-the-art performance for many *sequential prediction problems*, including those found in NLP and speech recognition. Sequential prediction problems can make predictions either for the entire sequence (sequence classification) or for each element within the sequence (sequence tagging or sequence labeling). More technically, RNNs use their internal hidden states h to process a sequence, such that the hidden state of any given timestep depends on the current input and the previous hidden state.

LSTM is a widely used variant of RNNs that is designed to learn long,

complex patterns within a sequence. Here, a complex pattern is one that can exhibit non-linear correlation among elements in a sequence. For example, noun-verb agreement in the English language can be complicated by prepositional phrases, so the phrase, "the idea of using many layers" is singular, even though the prepositional phrase ("of using many layers") is plural.

We use LSTM because it has been successfully applied to problems that are similar to our formulation of caching, which we describe in Section 3.2. For example, part-of-speech tagging and name-entity recognition in NLP are both sequence tagging tasks that aim to assign a label to each element of a sentence.

#### 3.1.3 Attention Mechanisms

LSTM has recently been coupled with *attention mechanisms*, which enable a sequence model to focus its attention on certain parts of the inputs. For example, when performing machine translation from a source language, say French, to a target language, say English, an attention mechanism could be used to learn the correlation between words in the original French sentence and its corresponding English translation [80]. As another example, in visual question answering systems, attention mechanisms have been used to focus on important parts of an image that are relevant to a particular question [79].

Mathematically, a typical attention mechanism quantifies the correlation between the hidden states  $h_t$  of the current step and all previous steps in the sequence using a scoring function which is then normalized with the Softmax function:

$$a_t(s) = \frac{exp(score(h_t, h_s))}{\sum_{s'} exp(score(h_t, h_{s'}))}$$

(3.1)

where  $a_t(s)$  is the attention weight that represents the impact of the past hidden state *s* on the current hidden state *t*. Different scoring functions can be chosen [80], and the attention weights are further applied to the past hidden states to obtain the context vector:

$$c_t = \sum_s a_{ts} h_s \tag{3.2}$$

The context vector represents the cumulative impact of all past hidden states on the current step, which along with the current hidden states  $h_t$  form the output of the current step.

#### 3.1.4 Hardware Constraints on the Predictor

There are three reasons why state-of-the-art machine learning models, including LSTM, are too resource-intensive to be deployed in hardware for problems such as cache replacement. First, the storage budget of hardware cache predictors is typically limited to 32 kilobytes [52, 121, 131]. Second, cache predictions must be generated in 20-30 CPU cycles (5-7 ns for a 4 GHz processor). Finally, the hardware predictor is required to converge after one training iteration (online training), as multiple training iterations increase latency, energy consumption, and storage.

In other resource-constrained applications of machine learning, online training is avoided by running inference on models that are pre-trained offline. However, pre-training is difficult for cache predictions because (1) most features are categorical and each program have a unique vocabulary set. (2) unlike static code analysis, the dynamic behavior of one program can vary significantly across different inputs.

### **3.2 Our Solution**

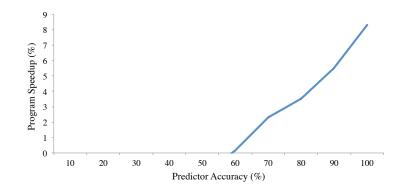

Our solution improves the accuracy of Hawkeye. Since Hawkeye learns from the optimal caching solution, improvements in the Hawkeye predictor's accuracy lead to replacement decisions that are closer to Belady's optimal solution, resulting in higher cache hit rates. Figure 3.2 shows the results of a limit study: We see that improving predictor accuracy leads to consistent improvements in program performance.

Figure 3.2: Improvements in predictor accuracy lead to increased speedup.

To improve predictor accuracy, we note that modern replacement policies [52, 67, 131], including Hawkeye, use limited program context—namely, the PC—to learn repetitive caching behavior. For example, if lines loaded by a given PC tend to be cache-friendly, then these policies will predict that future accesses by the

same PC will also be cache-friendly. Our work aims to improve prediction accuracy by exploiting richer dynamic program context, specifically, the sequence of past memory accesses that led to the current memory access. Thus, we formulate cache replacement as a *sequence labeling problem* where the goal is to label each access in a sequence with a binary label. More specifically, the input is a sequence of loads identified by their PC, and the goal is to learn whether a PC tends to access lines that are cache-friendly or cache-averse.

There are two reasons why we choose to identify loads by their PC instead of their memory address. First, there are fewer PCs, so they repeat more frequently than memory addresses, which speeds up training. Second, and more importantly, the size and learning time of LSTM both grow in proportion to the number of unique inputs, and since the number of unique addresses is  $100-1000 \times$  larger than the typical inputs for LSTM [80], the use of memory addresses is infeasible for LSTM.

We now summarize our three-step approach:

- 1. Unconstrained Offline Caching Model. First, we design an unconstrained caching model that is trained offline (see Section 3.2.1). Our offline model uses an LSTM with an attention mechanism that identifies important PCs in the input sequence. We show that this model significantly outperforms the state-of-the-art Hawkeye predictor.

- 2. **Offline Analysis.** Second, we analyze the attention layer and discover an important insight: Caching decisions depend primarily on the presence of a few memory accesses, not on the full ordered sequence (see Section 3.2.2).

Thus, we can encode our input feature (the history of PCs) more compactly so that the important memory accesses can be easily identified in hardware by a simple hardware-friendly linear model.

3. **Practical Online Model.** Third, we use the insights from our analysis to build a practical SVM model that is trained online to identify the few important PCs; this SVM model comes close to the accuracy of the much larger and slower LSTM (see Section 3.2.3). The online version of this SVM model is essentially a perceptron.

#### 3.2.1 LSTM with Scaled Attention

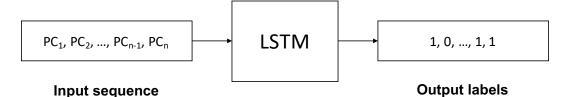

We now introduce our LSTM model that is designed for cache replacement. At a high level, our LSTM takes as input a sequence of load instructions and assigns as output a binary prediction to each element in the sequence, where the prediction indicates whether the corresponding load should be cached or not (see Figure 3.3).

Figure 3.3: Our LSTM-based sequence labeling model takes as input a sequence of PCs and produces as output cache-friendly (1) or cache-averse (0) labels.

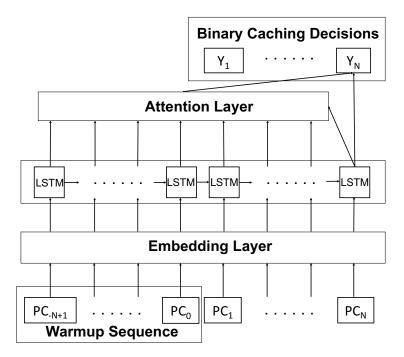

Figure 3.4 shows the network architecture of our LSTM model. We see that it consists of three layers: (1) an *embedding layer*, (2) a 1-layer LSTM, and (3) an attention layer. Since PCs are categorical in nature, our model uses a one-hot

Figure 3.4: The attention-based LSTM network architecture. LSTM handles a sequence of input recurrently.

representation for PCs,<sup>1</sup> where the size of the PC vocabulary is the total number of PCs in the program. However, the one-hot representation is not ideal for neural networks because it treats each PC equally. So to create learnable representations for categorical features like the PC, we use an embedding layer before the LSTM layer. The LSTM layer learns caching behavior, and on top of the LSTM we add a scaled attention layer to learn correlations among PCs; we describe this layer in Section 3.2.2. Figure 3.4 shows the attention layer at time step N.

Since the memory access trace is too long (see Table 3.3) for LSTM-based models, we first preprocess the trace by slicing it into fixed-length sequences of

<sup>&</sup>lt;sup>1</sup>A one-hot representation is a bit-vector with exactly one bit set.

| Benchmark | # Accesses | # PCs | # Addrs | Ave. # Accesses per PC | Ave. # Accesses per Addr |

|-----------|------------|-------|---------|------------------------|--------------------------|

| mcf       | 19.9M      | 650   | 0.87M   | 30K                    | 22.9                     |

| omnetpp   | 4.8M       | 1498  | 0.44M   | 3.2K                   | 10.9                     |

| soplex    | 9.4M       | 2348  | 0.39M   | 3.9K                   | 24.1                     |

| sphinx    | 3.0M       | 1698  | 0.11M   | 1.7K                   | 27.3                     |

| astar     | 1.2M       | 54    | 0.31M   | 22K                    | 3.8                      |

| lbm       | 5.0M       | 55    | 0.71M   | 90K                    | 7.0                      |

Table 3.1: Statistics for benchmarks used in offline analysis.

length 2N. To avoid losing context for the beginning of each slice of the trace, we overlap consecutive sequences by half of the sequence length N. The first half of each sequence is thus a warmup sequence that provides context for the predictions of the second half of the sequence. In particular, for a memory access sequence  $PC_{-N+1}$ , ...,  $PC_N$ , the first half of the sequence  $PC_{-N+1}$  to  $PC_0$  provides context of at least length N for  $PC_1$  to  $PC_N$ . During training and testing, only the output decisions  $Y_1$  to  $Y_N$  for time step 1, ..., N are collected from this sequence. Table 3.3.6 shows our specific hyper-parameters.

#### 3.2.2 Insights from Our LSTM Model

Our LSTM model is effective but impractical, so we conduct several experiments to understand why our LSTM works well. First, we note that the LSTM's accuracy improves as we increase the PC history length from 10 to 30, and the accuracy benefits saturate at a history length of 30 (see Figure 3.15). This leads us to our first observation:

*Observation* 1. Our model benefits from a long history of past PCs, in particular, the past 30 PCs.

To gain even deeper insights into our attention-based LSTM model, we use the scaled attention mechanism to find the source of its accuracy. Our analysis of the attention layer reveals that while the history of PCs is a valuable feature, a completely ordered representation of the PC history is unnecessary. We now explain how we designed the attention layer so that it would reveal insights.

Attention Layer Design. Our attention layer uses the state-of-the-art attention mechanism with scaling [123] (see Equation 3.3). Our scaled attention layer uses a scaled dot-product to compute the *attention weight vector*  $a_t$ , which captures the correlation between the *target element* and the *source elements* in the sequence; we define a target element to be the load instruction for which the model will make a prediction, and we define the source elements to be the past load instructions in the sequence that the model uses to make the prediction. Specifically,  $a_t$  is computed by first using a scoring function to compare the hidden states of the current target  $h_t$  against each source element  $h_s$ , before then scaling with a factor f and normalizing the scores to a distribution using the softmax function. The attention weight vector is then used to compute a context vector,  $c_t$ , which is concatenated with  $h_t$  to determine the output decision. In this work, we use the dot product as the scoring function.

$$a_t(s) = \frac{exp(f \cdot score(h_t, h_s))}{\sum_{s'} exp(f \cdot score(h_t, h_{s'}))}$$

(3.3)

While the attention's scaling factor was originally used to deal with the growing magnitude of dot products with the input dimension [123], we find a new

use of the scaling factor: A moderate increase in the scaling factor forces sparsity in the attention weight vectors but has minimal influence on accuracy. A sparse attention weight vector indicates that only a few source elements in the sequence influence the prediction. For our caching model, we would expect the attention weights to quantify the correlation between the *target memory access* at time step N and the *source memory accesses* from timesteps 1 to N - 1. Unfortunately, we find that the attention layer without scaling (or scaling factor of 1) presents a nearly uniform attention weight distribution, thus providing little useful information. To avoid this uniform distribution, we increase the scaling factor f to force the sparsity in attention weight distribution, thereby revealing dependences between source accesses and target access.

Figure 3.5: Cumulative distribution function of attention weight distribution for omnetpp.

**Insights From The Scaled Attention Layer.** Figure 3.5 shows for one benchmark the cumulative distribution function of the attention weight distributions with different scaling factors. Surprisingly, we see that without losing accuracy, the scaled attention weight distribution becomes biased towards a few source accesses, which shows that our model can make correct predictions based on just a few source memory accesses.

Figure 3.6: Attention weight vectors of consecutive memory accesses. The y-axis shows the indices of target memory accesses, and the x-axis shows the offset of source memory accesses from the target. The white boxes show that target memory accesses are strongly correlated with just a few source memory accesses.

Figures 3.6show the attention weight distributions for 100 and 10 consecutive memory accesses, respectively. Each row represents the attention weight vector for one target memory access; white boxes indicate strong correlation between source and target, and black boxes indicate weak correlation. Figure 3.6 shows that the same source memory access has dominant attention weights for nearly every target, forming an oblique line as its offset increases with the row index. Therefore, we obtain our second observation: