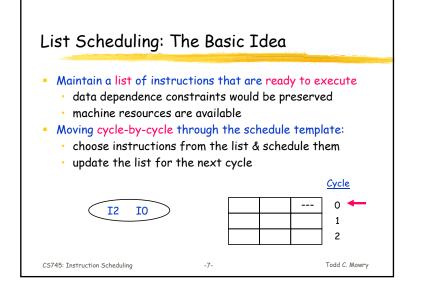

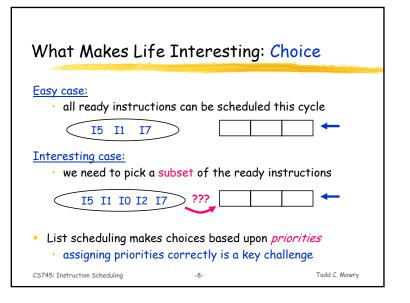

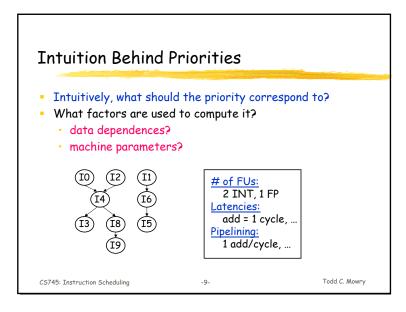

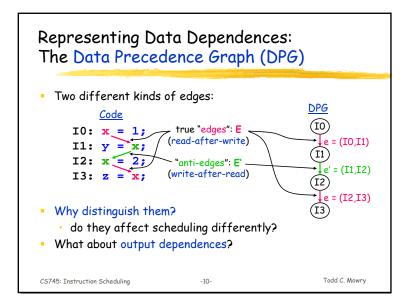

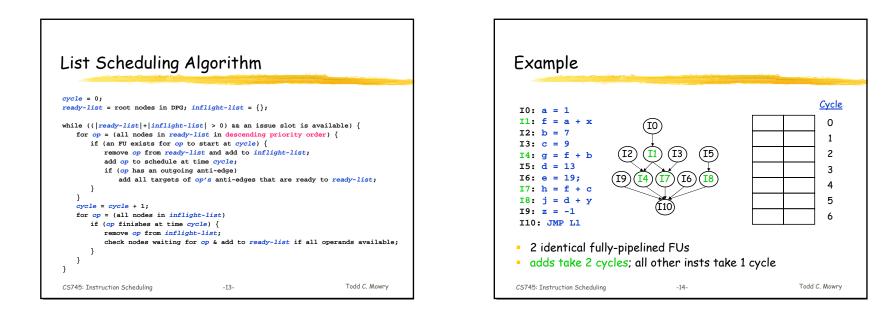

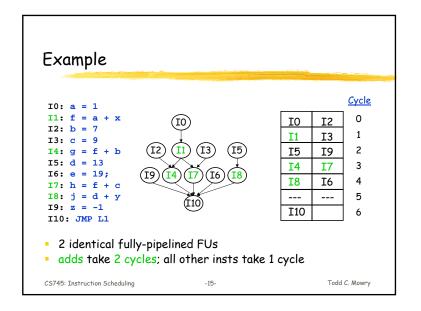

## List Scheduling Algorithm: Inputs and Outputs Algorithm reproduced from: "An Experimental Evaluation of List Scheduling", Keith D. Cooper, Philip J. Schielke, and Devika Subramanian. Rice University, Department of Computer Science Technical Report 98-326, September 1998. Inputs: Output: Data Precedence Machine Scheduled Code Cycle Graph (DPG) Parameters 10 I2 0 # of FUs: ---(I2` (I1) 2 INT, 1 FP **I**1 **I**4 1 ----(I6)Latencies: I3 2 **I8 I**6 add = 1 cycle, ... I10 ----I11 3 Pipelining: 17 19 I5 4 1 add/cycle, ... Todd C. Mowry CS745: Instruction Scheduling -6-