# Foundations: Synchronization Execution Abstractions

Chris Rossbach CS378

# Today

- Questions?

- Administrivia

- Lab 1 due sooner than you'd like

- Foundations

- Threads/Processes/Fibers

- Cache coherence (maybe)

- Acknowledgments: some materials in this lecture borrowed from

- Emmett Witchel (who borrowed them from: Kathryn McKinley, Ron Rockhold, Tom Anderson, John Carter, Mike Dahlin, Jim Kurose, Hank Levy, Harrick Vin, Thomas Narten, and Emery Berger)

- Andy Tannenbaum

Faux Quiz (answer any 2, 5 min)

- What is the maximum possible speedup of a 75% parallelizable program on 8 CPUs

- What is super-linear speedup? List two ways in which super-linear speedup can occur.

- What is the difference between strong and weak scaling?

- Define Safety, Liveness, Bounded Waiting, Failure Atomicity

- What is the difference between processes and threads?

- What's a fiber? When and why might fibers be a better abstraction than threads?

# Review: correctness conditions

- Safety

- Only one thread in the critical region

- Liveness

- Some thread that enters the entry section eventually enters the critical region

- Even if other thread takes forever in non-critical region

- Bounded waiting

- A thread that enters the entry section enters the critical section within some bounded number of operations.

- If a thread i is in entry section, then there is a bound on the number of times that other threads are allowed to enter the critical section before thread i's request is granted

while (1)

Mutex, spinlock, etc. are ways to implement

Did we get all the important conditions? Why is correctness defined in terms of locks? Theorem: Every property is a combination of a safety property and a liveness property. -Bowen Alpern & Fred Schneider https://www.cs.cornell.edu/fbs/publications/defliveness.pdf

Entry section

Exit section

Critical section

Non-critical section

### Processes and Threads and Fibers...

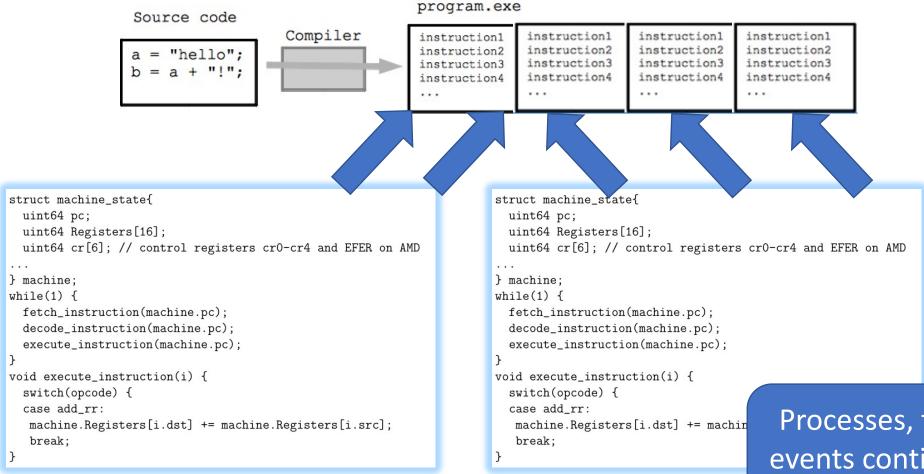

### Programming and Machines: a mental model

```

struct machine_state{

uint64 pc;

uint64 Registers[16];

uint64 cr[6]; // control registers cr0-cr4 and EFER on AMD

. . .

} machine;

while(1) {

fetch_instruction(machine.pc);

decode_instruction(machine.pc);

execute_instruction(machine.pc);

}

void execute_instruction(i) {

switch(opcode) {

case add_rr:

machine.Registers[i.dst] += machine.Registers[i.src];

break;

}

```

| prev instruct  | prev instruct  | prev instruct |   |     |

|----------------|----------------|---------------|---|-----|

| load A(1)      | call funcD     | do 10 i=1,N   |   |     |

| load B(1)      | x=y*z          | alpha=w**3    |   | tim |

| C(1)=A(1)*B(1) | sum=x*2        | zeta=C(i)     |   | me  |

| store C(1)     | call sub1(i,j) | 10 continue   |   |     |

| next instruct  | next instruct  | next instruct | Ľ |     |

| P1             | P2             | Pn            |   |     |

### Parallel Machines: a mental model

Processes, threads, fibers, events continuations, ... are all abstractions for this

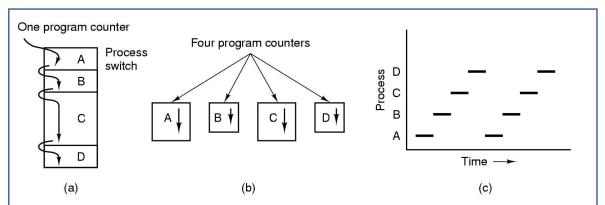

### Processes

Model

- Multiprogramming of four programs

- Conceptual model of 4 independent, sequential processes

- Only one program active at any instant

### Implementation

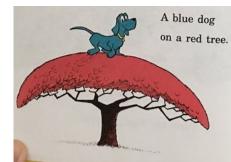

| Process management        | Memory management        | File management   |

|---------------------------|--------------------------|-------------------|

| Registers                 | Pointer to text segment  | Root directory    |

| Program counter           | Pointer to data segment  | Working directory |

| Program status word       | Pointer to stack segment | File descriptors  |

| Stack pointer             |                          | User ID           |

| Process state             |                          | Group ID          |

| Priority                  |                          |                   |

| Scheduling parameters     |                          |                   |

| Process ID                |                          |                   |

| Parent process            |                          |                   |

| Process group             |                          |                   |

| Signals                   |                          |                   |

| Time when process started |                          |                   |

| CPU time used             |                          |                   |

| Children's CPU time       |                          |                   |

| Time of next alarm        |                          |                   |

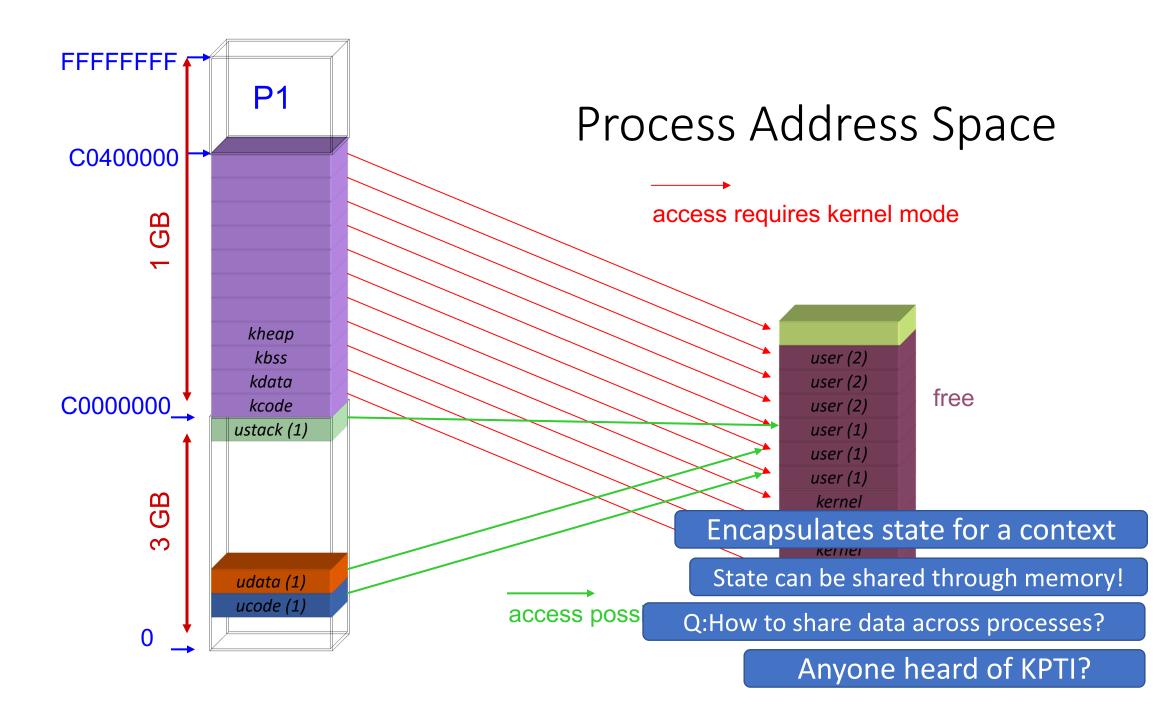

# Abstractions for Concurrency

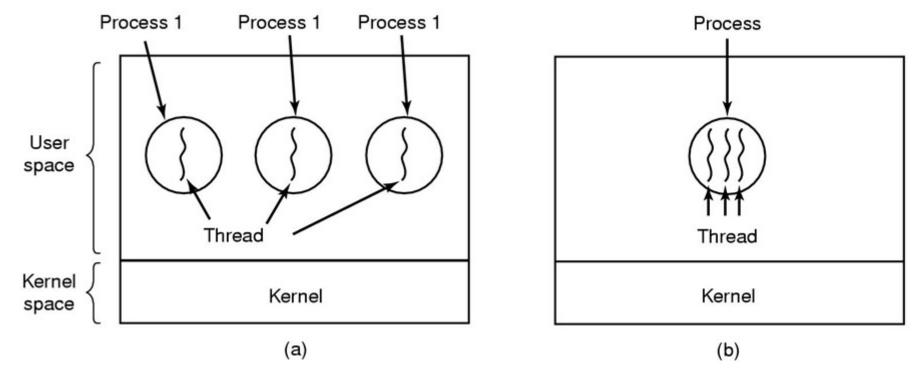

(a) Three processes each with one thread

(b) One process with three threads

When might (a) be better than (b)? Vice versa? Could you do lab 1 with processes instead of threads? Threads simplify sharing and reduce context overheads

# Using threads

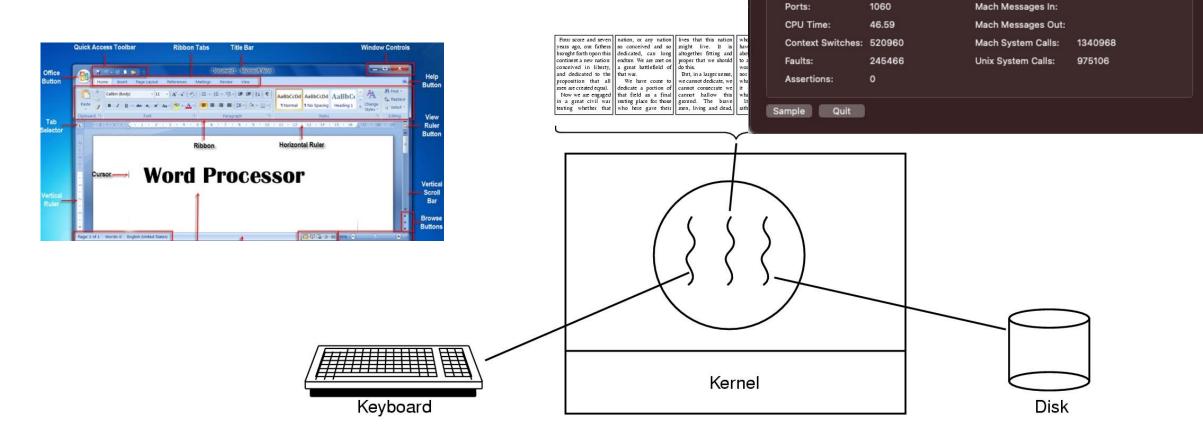

### Ex. How might we use threads in a word processo

.

% CPU:

Threads:

Parent Process: launchd (1)

Process Group: Microsoft Word (446)

0.63

Memory

15

Microsoft Word (446)

Statistics

User: rossbach (501)

**Open Files and Ports**

467

Recent hangs: 0

Page Ins:

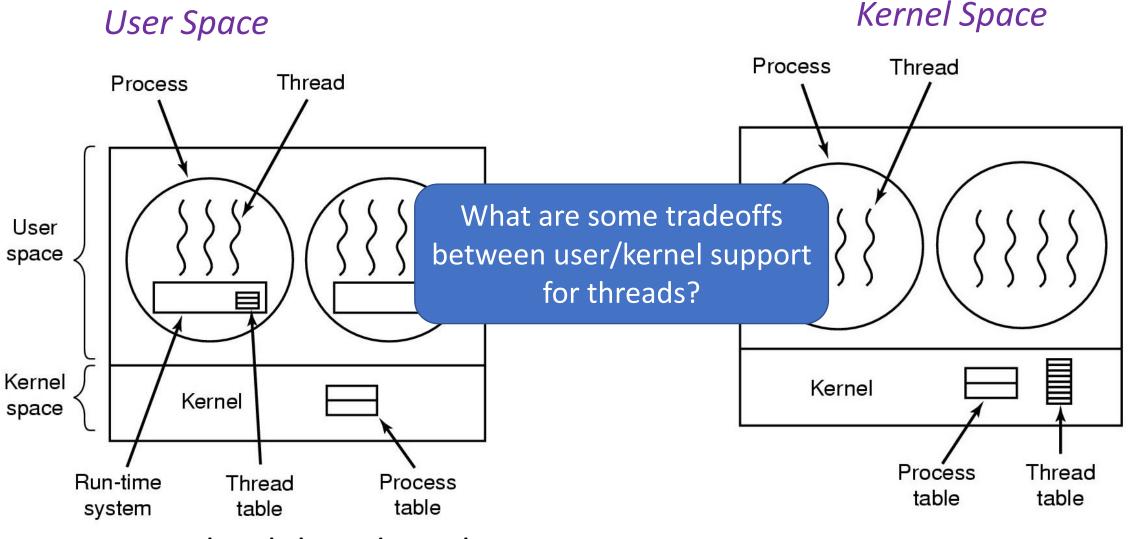

### Where to Implement Threads:

A user-level threads package

A threads package managed by the kernel

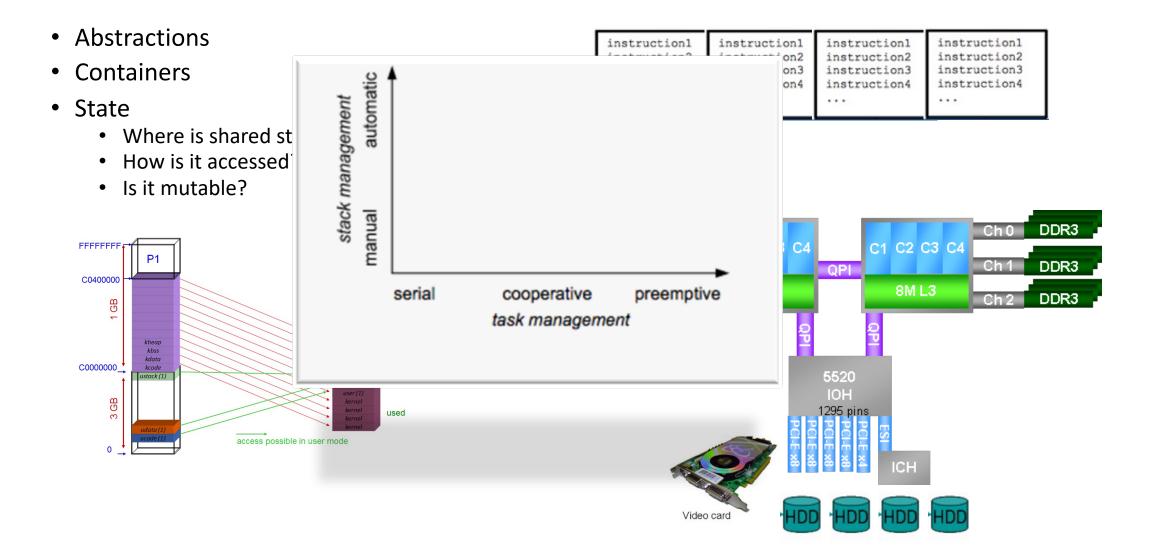

# **Execution Context Management**

"Task" == "Flow of Control", but with less typing "Stack" == Task State

### Task Management

- Preemptive

- Interleave on uniprocessor

- Overlap on multiprocessor

- Serial

- One at a time, no conflict

- Cooperative

- Yields at well-defined points

- E.g. wait for long-running I/O

### Stack Management

- Manual

- Inherent in Cooperative

- Changing at quiescent points

- Automatic

- Inherent in pre-emptive

- Downside: Hidden concurrency assumptions

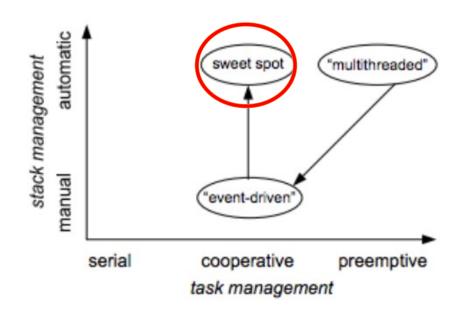

# These dimensions can be orthogonal

# Fibers: the Sweet Spot?

- Cooperative tasks

- most desirable when reasoning about concurrency

- usually associated with event-driven programming

- Automatic stack management

- most desirable when reading/maintaining code

- Usually associated with threaded (or serial) programming

Fibers: cooperative threading with automatic stack management

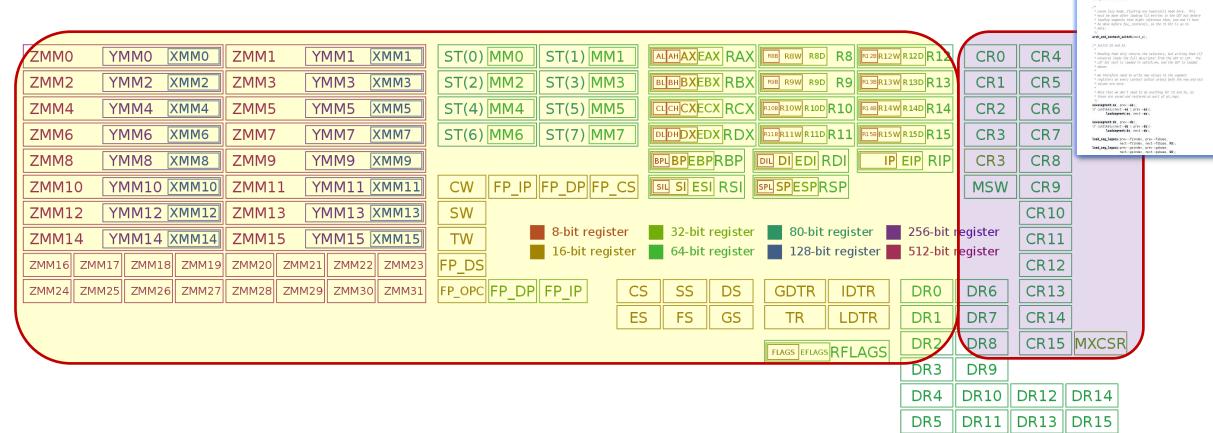

# Threads vs Fibers

- Like threads, just an abstraction for flow of control

- *Lighter weight* than threads

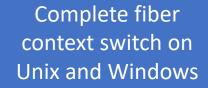

- In Windows, just a stack, subset of arch. registers, non-preemptive

- \*Not\* just threads without exception support

- stack management/impl has interplay with exceptions

- Can be completely exception safe

- *Takeaway*: diversity of abstractions/containers for execution flows

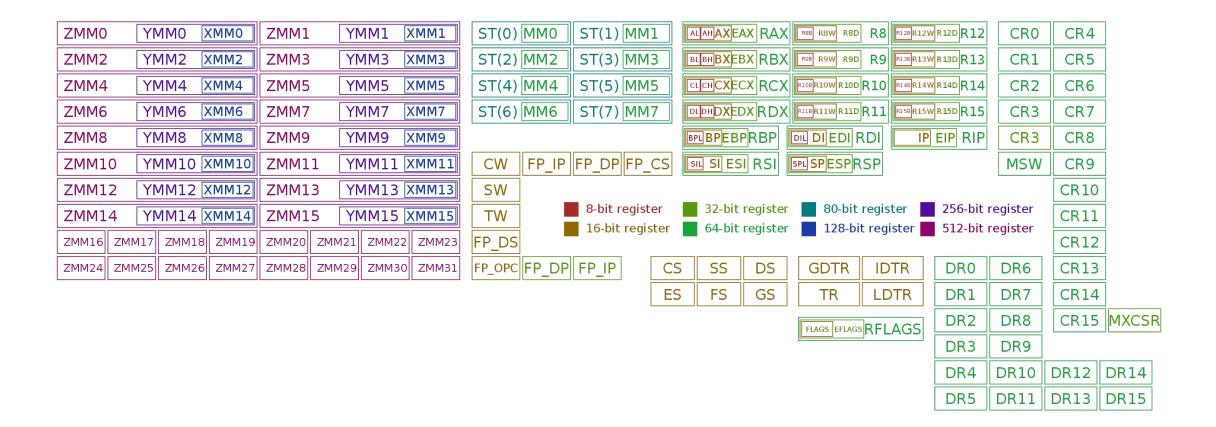

### x86\_64 Architectural Registers

• Register map diagram courtesy of: By Immae - Own work, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=32745525

- $switch_to(x,y)$  should switch tasks from x to y.

- \* This could still be optimized:

- \* fold all the options into a flag word and test it with a single test

- \* could test fs/gs bitsliced

\*

\*

- \* Kprobes not supported here. Set the probe on schedule inst \* Function graph tracer not supported too.

- \_\_visible \_\_notrace\_funcgraph struct task\_struct \*

struct thread\_struct \*prev = &prev p->thread; struct thread\_struct \*next = &next\_p->thread; struct fpu \*prev\_fpu = &prev->fpu; struct fpu \*next\_fpu = &next->fpu; int cpu = smp\_processor\_id() struct tss\_struct \*tss = &per\_cpu(cpu\_tss\_rw, cpu);

WARN\_ON\_ONCE(IS\_ENABLED(CONFIG\_DEBUG\_ENTRY) && this\_cpu\_read(irq\_count) != -1);

### switch\_fpu\_prepare(prev\_fpu, cpu);

- /\* We must save %fs and %gs before load\_TLS() because \* %fs and %gs may be cleared by load\_TLS().

- \* (e.g. xen\_load\_tls())

### save\_fsgs(prev\_p);

\* Load TLS before restoring any segments so that segment loads \* reference the correct GDT entries.

### load\_TLS(next, cpu);

\* Leave lazy mode, flushing any hypercalls made here. This \* must be done after loading TLS entries in the GDT but before \* loading segments that might reference them, and and it must \* be done before fpu\_\_restore(), so the TS bit is up to \* date. \*/

### arch\_end\_context\_switch(next\_p);

/\* Switch DS and ES.

\* Reading them only returns the selectors, but writing them (if \* nonzero) loads the full descriptor from the GDT or LDT. The \* LDT for next is loaded in switch\_mm, and the GDT is loaded \* above. \*

\* We therefore need to write new values to the segment

- \* registers on every context switch unless both the new and old \* values are zero.

\* Note that we don't need to do anything for CS and SS, as \* those are saved and restored as part of pt\_regs. \*/

savesegment(es, prev->es); if (unlikely(next->es | prev->es)) loadsegment(es, next->es);

### savesegment(ds, prev->ds); if (unlikely(next->ds | prev->ds)) loadsegment(ds, next->ds);

load\_seg\_legacy(prev->fsindex, prev->fsbase, next->fsindex, next->fsbase, FS); load\_seg\_legacy(prev->gsindex, prev->gsbase, next->gsindex, next->gsbase, GS

### Linux x86\_64 context switch *excerpt*

MXCSR

**DR14**

**DR15**

|                                | * The AMD64 are                                                                                 | chitecture provides :                      | 16 general 64-bit re                    | gisters together with 16                |  |

|--------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------|-----------------------------------------|--|

|                                | * 128-bit SSE                                                                                   | registers, overlappi                       | ng with 8 legacy 80-                    | bit x87 floating point                  |  |

| ST(0) MM0 ST(1) MM1            | * registers.<br>*                                                                               |                                            |                                         |                                         |  |

|                                | *                                                                                               | Both                                       | Unix only                               | Windows only                            |  |

| ST(2) MM2 ST(3) MM3            | *                                                                                               |                                            |                                         |                                         |  |

|                                | * rax                                                                                           | Result register                            |                                         |                                         |  |

| ST(4) MM4 ST(5) MM5            | * rbx                                                                                           | Must be preserved                          | 000000000000000000000000000000000000000 | 0.0000000000000000000000000000000000000 |  |

|                                | * rcx                                                                                           |                                            | Fourth argument                         | First argument                          |  |

| ST(6) MM6 ST(7) MM7            | * rdx                                                                                           | Charle and then much                       | Third argument                          | Second argument                         |  |

|                                | * rsp<br>* rbp                                                                                  | Stack pointer, must<br>Frame pointer, must |                                         |                                         |  |

|                                | * rsi                                                                                           | frame poincer, musc                        | Second argument                         | Must be preserved                       |  |

|                                | * rdi                                                                                           |                                            | First argument                          | Must be preserved                       |  |

| CW FP_IP FP_DP FP_C            | * r8                                                                                            |                                            | Fifth argument                          | Third argument                          |  |

| SW                             | * r9                                                                                            |                                            | Sixth argument                          | Fourth argument                         |  |

|                                | * r10-r11                                                                                       | Volatile                                   |                                         |                                         |  |

| TW 8-bit registe               | * r12-r15                                                                                       | Must be preserved                          |                                         |                                         |  |

| 16-bit regist                  | * xmm0-5                                                                                        | Volatile                                   |                                         |                                         |  |

| P DS                           | * xmm6-15                                                                                       |                                            | Volatile                                | Must be preserved                       |  |

| F_05                           | * fpcsr                                                                                         | Non volatile                               |                                         |                                         |  |

| P_OPC FP DP FP IP              | * mxcsr                                                                                         | Non volatile                               |                                         |                                         |  |

|                                |                                                                                                 | two pachitactures w                        | o oct slight]v diffo                    | mont lists of posistops                 |  |

|                                | * Thus for the two architectures we get slightly different lists of registers<br>* to preserve. |                                            |                                         |                                         |  |

| *                              |                                                                                                 |                                            |                                         |                                         |  |

| * Registers "owned" by caller: |                                                                                                 |                                            |                                         |                                         |  |

|                                | * Unix: rbx, rsp, rbp, r12-r15, mxcsr (control bits), x87 CW                                    |                                            |                                         |                                         |  |

|                                | * Windows: rbx, rsp, rbp, rsi, rdi, r12-r15, xmm6-15                                            |                                            |                                         |                                         |  |

|                                | *                                                                                               |                                            |                                         |                                         |  |

|                                |                                                                                                 |                                            |                                         | DR4                                     |  |

|                                          |                                             |                              |           |    | CR0    | CR4  | ŀ  |

|------------------------------------------|---------------------------------------------|------------------------------|-----------|----|--------|------|----|

| Both                                     | Unix only                                   | Windows only                 |           |    | CR1    | CR5  |    |

| Result register<br>Must be preserved     |                                             |                              |           |    | CR2    | CR6  |    |

|                                          | Fourth argument<br>Third argument           | First argume<br>Second argum |           |    | CR3    | CR7  | ,  |

| Stack pointer, mus<br>Frame pointer, mus |                                             | Must be pres                 | erved     | j  | CR3    | CR8  | }  |

|                                          | First argument<br>Fifth argument            | Must be pres<br>Third argume | erved     |    | MSW    | CR9  | )  |

| Volatile                                 | Sixth argument                              | Fourth argum                 | ent       |    |        | CR1  | C  |

| Must be preserved<br>Volatile            |                                             |                              |           |    | gister | CR1  | 1  |

| Non volatile                             | Volatile                                    | Must be pres                 | erved     | re | gister | CR1  | 2  |

| Non volatile                             |                                             |                              |           |    | DR6    | CR1  | 3  |

| e two architectures                      | we get slightly dif                         | ferent lists of              | registers |    | DR7    | CR14 | 4  |

| owned" by caller:                        |                                             |                              |           |    | DR8    | CR1  | 5  |

|                                          | l-r15, mxcsr (contro<br>, rdi, r12-r15, xmm |                              |           |    | DR9    |      |    |

|                                          |                                             |                              | DR4       |    | DR10   | DR12 |    |

|                                          |                                             |                              | DR5       |    | DR11   | DR13 | 1ľ |

wn work, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=32745525

ZMM0 ZMM2 ZMM4 ZMM6 ZMM8 **ZMM10 ZMM12** ZMM14 ZMM16 ZMM ZMM24 ZMM

Red

/\* switch\_to(x,y) should switch tasks from x to y. \* This could still be extinized: \* fold all the extinuis into a flag word and test it with a single test. - could test flygs bisiles.

Xprobes not supported here. Set the probe on schedule instead. Function graph tracer not supported too. / /sible \_\_notrace\_funcgraph struct task\_struct \*

'/

\_visible \_\_netrace\_funcgraph struct task\_struct '

\_\_switch\_te(struct task\_struct 'prev\_p, struct task\_struct 'next\_p)

{

struct thread\_struct "prev = Sprev\_p->thread; struct thread\_struct "next = Snot\_p->thread; struct fpu "prev\_fpu = Sprev->fpu; struct fpu "next\_fpu = Snext->fpu; int cpu = mo\_precessor.id();

struct tes\_struct \*tss = &per\_cpu(epu\_tes\_rw, cpu); struct tes\_struct \*tss = &per\_cpu(epu\_tes\_rw, cpu); wahn\_ow\_owce(ts\_bualleb(confic\_Debug\_Diffw)) &s this\_cpu\_read(ira\_count) != -1);

### switch\_fpu\_prepare(prev\_fpu, cpu);

/\* We must save %fs and %gs before load\_TLS() because \* %fs and %gs may be cleared by load\_TLS(). \* \* \* (e.e. yen load tls())

save\_fsgs(prev\_p);

Load TLS before restaring any segments so that segment l \* reference the correct CDT entries. \*/ lad\_TLS(rest, cpu);

### x86 64 Registers and Threads

• Register map diagram courtesy of: By Immae - Own work, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=32745525

<sup>•</sup> Register map diagram courtesy of: By Immae - Own work, CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=32745525

### Pthreads

- POSIX standard thread model,

- Specifies the API and call semantics.

- Popular most thread libraries are Pthreads-compatible

### Preliminaries

- Include pthread.h in the main file

- Compile program with -lpthread

- gcc -o test test.c -lpthread

- may not report compilation errors otherwise but calls will fail

- Good idea to check return values on common functions

### Thread creation

- Types: pthread\_t type of a thread

- Some calls:

- No explicit parent/child model, except main thread holds process info

- Call pthread\_exit in main, don't just fall through;

- When do you need pthread\_join ?

- status = exit value returned by joinable thread

- Detached threads are those which cannot be joined (can also set this at creation)

### Creating multiple threads

```

#include <stdio.h>

#include <pthread.h>

#define NUM THREADS 4

void *hello (void *arg) {

printf("Hello Thread\n");

main() {

pthread t tid[NUM THREADS];

for (int i = 0; i < NUM THREADS; i++)

pthread create(&tid[i], NULL, hello, NULL);

for (int i = 0; i < NUM THREADS; i++)</pre>

pthread_join(tid[i], NULL);

```

# Can you find the bug here?

### What is printed for myNum?

```

void *threadFunc(void *pArg) {

int* p = (int*)pArg;

int myNum = *p;

printf( "Thread number %d\n", myNum);

}

. . .

// from main():

for (int i = 0; i < numThreads; i++) {

pthread_create(&tid[i], NULL, threadFunc, &i);

}</pre>

```

### Pthread Mutexes

- Type: pthread\_mutex\_t

- Attributes: for shared mutexes/condition vars among processes, for priority inheritance, etc.

- use defaults

- Important: Mutex scope must be visible to all threads!

### Pthread Spinlock

- Type: pthread\_spinlock\_t

- int pthread\_spinlock\_init(pthread\_spinlock\_t \*lock); int pthread\_spinlock\_destroy(pthread\_spinlock\_t \*lock); int pthread\_spin\_lock(pthread\_spinlock\_t \*lock); int pthread\_spin\_unlock(pthread\_spinlock\_t \*lock); int pthread\_spin\_trylock(pthread\_spinlock\_t \*lock);

Wait...what's the difference?

int pthread\_mutex\_init(pthread\_mutex\_t \*mutex,...); int pthread\_mutex\_destroy(pthread\_mutex\_t \*mutex); int pthread\_mutex\_lock(pthread\_mutex\_t \*mutex); int pthread\_mutex\_unlock(pthread\_mutex\_t \*mutex); int pthread\_mutex\_trylock(pthread\_mutex\_t \*mutex);

# Review: correctness conditions

- Safety

- Only one thread in the critical region

- Liveness

- Some thread that enters the entry section eventually enters the critical region

- Even if other thread takes forever in non-critical region

- Bounded waiting

- A thread that enters the entry section enters the critical section within some bounded number of operations.

- If a thread i is in entry section, then there is a bound on the number of times that other threads are allowed to enter the critical section before thread i's request is granted

while (1)

Mutex, spinlock, etc. are ways to implement

Did we get all the important conditions? Why is correctness defined in terms of locks? Theorem: Every property is a combination of a safety property and a liveness property. -Bowen Alpern & Fred Schneider https://www.cs.cornell.edu/fbs/publications/defliveness.pdf

Entry section

Exit section

Critical section

Non-critical section

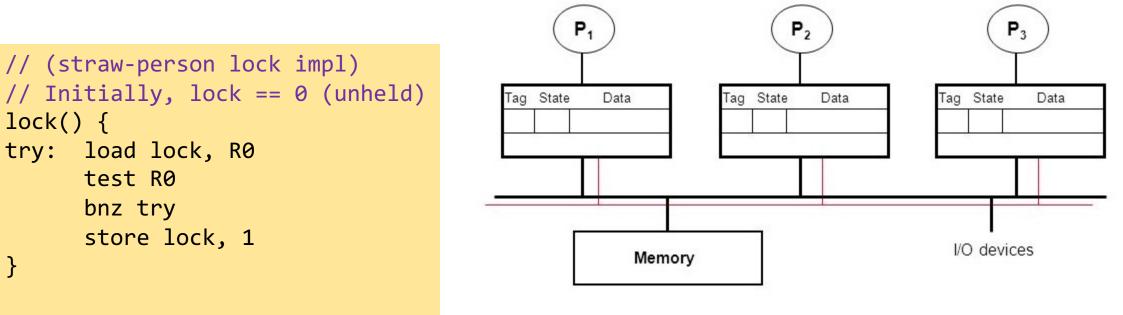

### Implementing Locks

int lock\_value = 0; int\* lock = &lock\_value;

```

Lock::Acquire() {

while (*lock == 1)

; //spin

*lock = 1;

}

```

Completely and utterly broken. How can we fix it?

Lock::Release() {

\*lock = 0;

}

### What are the problem(s) with this?

- ➤ A. CPU usage

- ➤ B. Memory usage

- C. Lock::Acquire() latency

- D. Memory bus usage

- E. Does not work

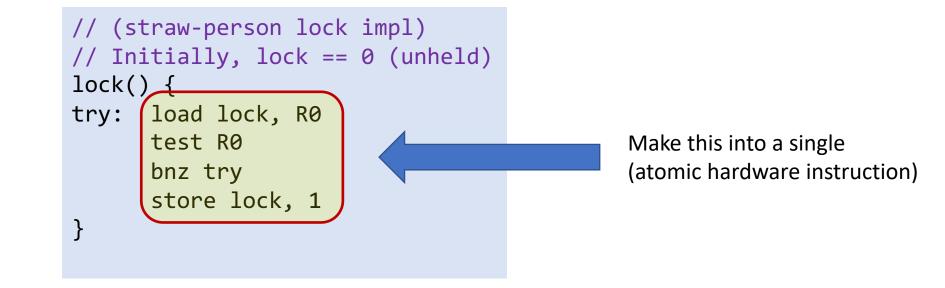

# HW Support for Read-Modify-Write (RMW)

IDEA: hardware implements something like:

```

bool rmw(addr, value) {

atomic {

tmp = *addr;

newval = modify(tmp);

*addr = newval;

}

}

```

Why is that hard? How can we do it? Preview of Techniques:

- Bus locking

- Single Instruction ISA extensions

- Test&Set

- CAS: Compare & swap

- Exchange, locked increment, locked decrement (x86)

- Multi-instruction ISA extensions:

- LLSC: (PowerPC, Alpha, MIPS)

- Transactional Memory (x86, PowerPC)

### Implementing Locks with Test&set

int lock\_value = 0; int\* lock = &lock\_value;

Lock::Acquire() { while (test&set(lock) == 1) ; //spin }

### (test & set ~= CAS ~= LLSC) TST: *Test&set*

- Reads a value from memory

- Write "1" back to memory location

Lock::Release() {

\*lock = 0;

}

### What are the problem(s) with this?

- ➤ A. CPU usage

- ➢ B. Memory usage

- C. Lock::Acquire() latency

- D. Memory bus usage

- E. Does not work

### More on this later...

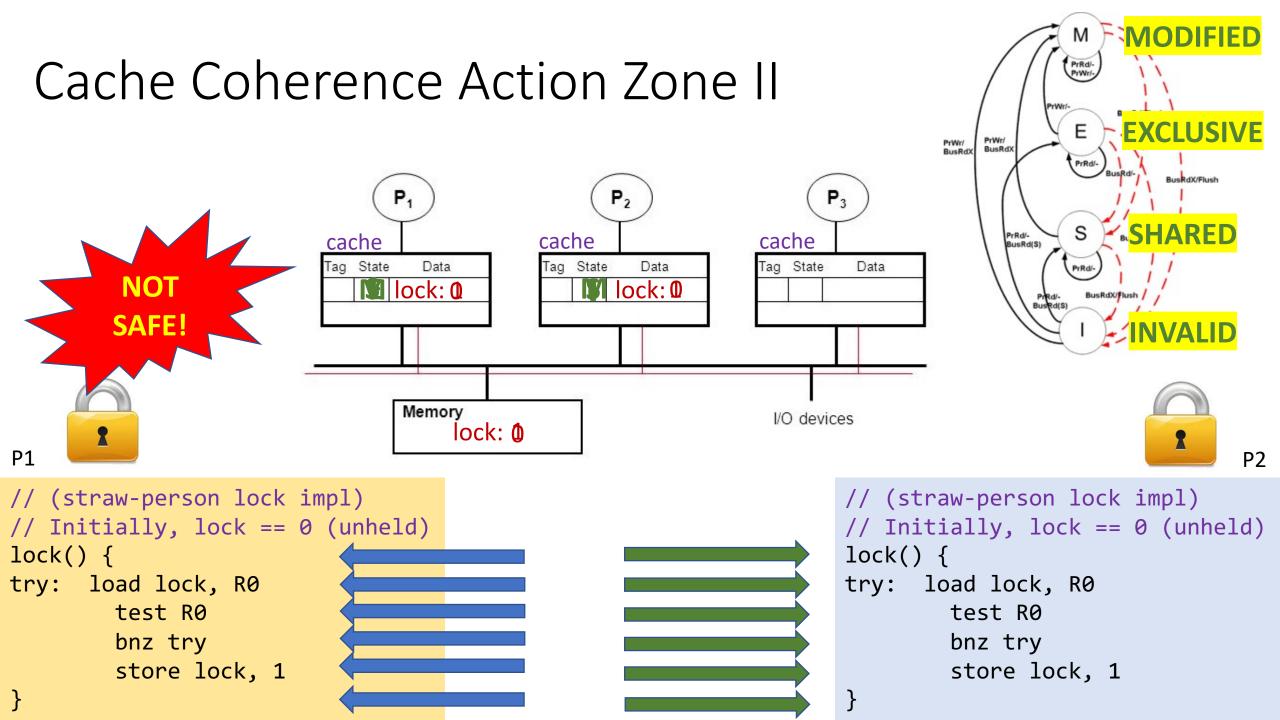

Multiprocessor Cache Coherence

# PhysicsConcurrencyF = ma~ coherence

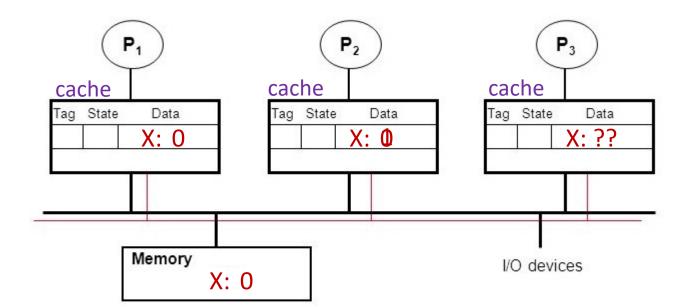

### Multiprocessor Cache Coherence

- P1: read X

- P2: read X

- P2: X++

- P3: read X

# Multiprocessor Cache Coherence

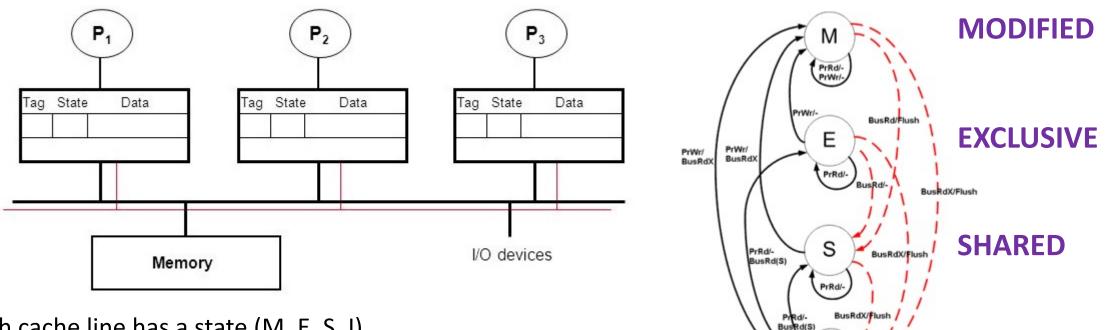

INVALID

Each cache line has a state (M, E, S, I)

- Processors "snoop" bus to maintain states

- Initially  $\rightarrow$  'l'  $\rightarrow$  Invalid

- Read one  $\rightarrow$  'E'  $\rightarrow$  exclusive

- Reads  $\rightarrow$  'S'  $\rightarrow$  multiple copies possible

- Write  $\rightarrow$  'M'  $\rightarrow$  single copy  $\rightarrow$  lots of cache coherence traffic

# Read-Modify-Write (RMW)

- Implementing locks requires read-modify-write operations

- Required effect is:

- An atomic and isolated action

- 1. read memory location AND

- 2. write a new value to the location

- RMW is *very tricky* in multi-processors

- Cache coherence alone doesn't solve it

## Essence of HW-supported RMW

# HW Support for Read-Modify-Write (RMW)

| Test & Set                                                                                                                        | CAS                                                                                                                                                  | Exchange, locked increment/decrement,                                                                    | LLSC: load-linked store-conditional                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Most architectures                                                                                                                | Many architectures                                                                                                                                   | x86                                                                                                      | PPC, Alpha, MIPS                                                                                                                                  |

| <pre>int TST(addr) {     atomic {         ret = *addr;         if(!*addr)            *addr = 1;         return ret;     } }</pre> | <pre>bool cas(addr, old, new) {    atomic {      if(*addr == old) {         *addr = new;         return true;      }      return false;    } }</pre> | <pre>int XCHG(addr, val) {    atomic {      ret = *addr;      *addr = val;      return ret;    } }</pre> | <pre>bool LLSC(addr, val) {   ret = *addr;   atomic {     if(*addr == ret) {       *addr = val;       return true;     }    return false; }</pre> |

```

void CAS_lock(lock) {

while(CAS(&lock, 0, 1) != true);

}

```

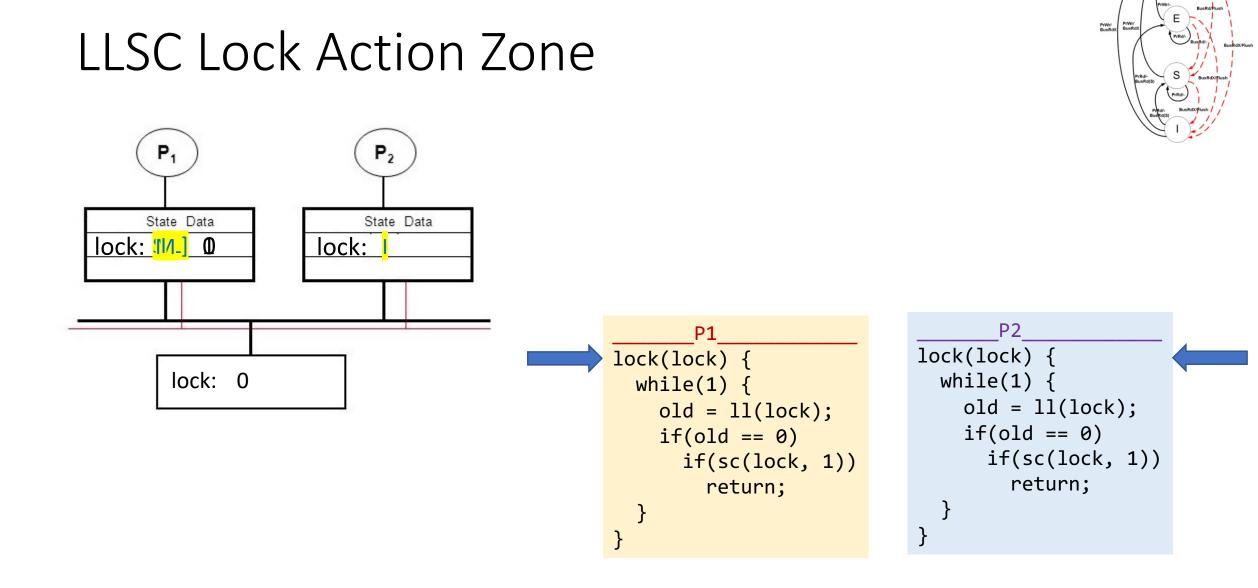

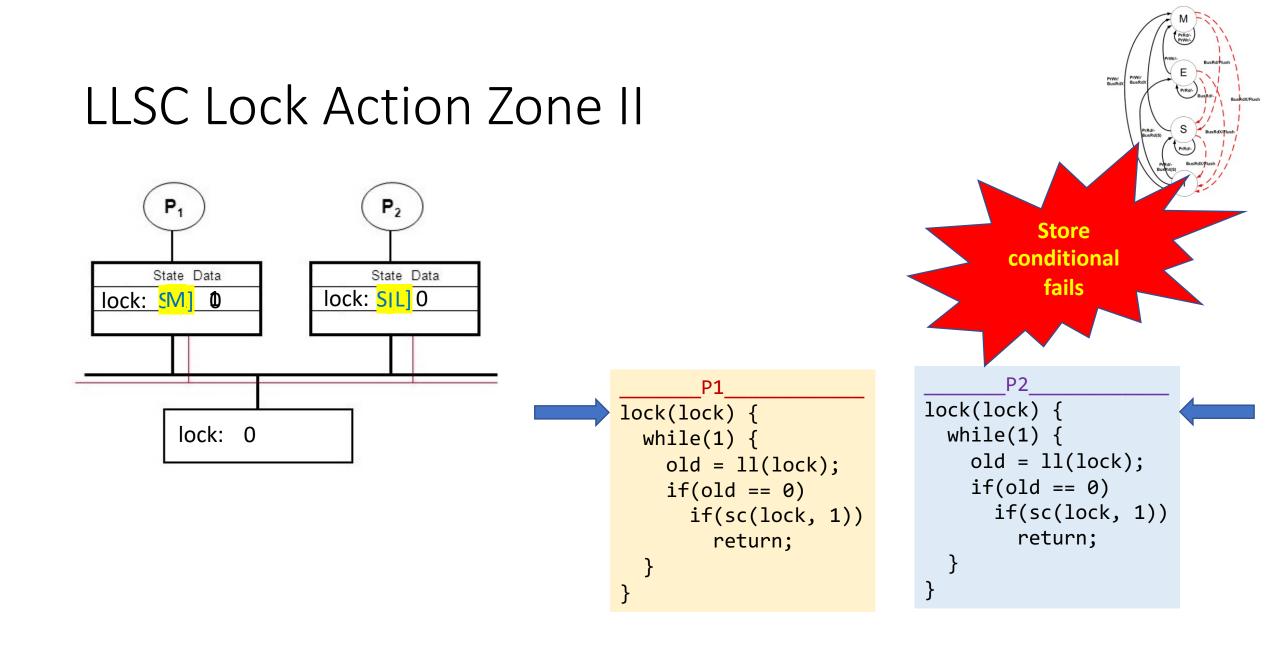

## HW Support for RMW: LL-SC

```

LLSC: load-linked store-conditional

PPC, Alpha, MIPS

bool LLSC(addr, val) {

ret = *addr;

atomic {

if(*addr == ret) {

*addr = val;

return true;

}

return false;

}

```

```

void LLSC_lock(lock) {

while(1) {

old = load-linked(lock);

if(old == 0 && store-cond(lock, 1))

return;

}

}

```

- load-linked is a load that is "linked" to a subsequent store-conditional

- Store-conditional only succeeds if value from linked-load is unchanged

## Implementing Locks with Test&set

int lock\_value = 0; int\* lock = &lock\_value;

Lock::Acquire() { while (test&set(lock) == 1) ; //spin }

(test & set ~ CAS ~ LLSC)

```

Lock::Release() {

*lock = 0;

}

```

#### What is the problem with this?

- > A. CPU usage B. Memory usage C. Lock::Acquire() latency

- D. Memory bus usage E. Does not work

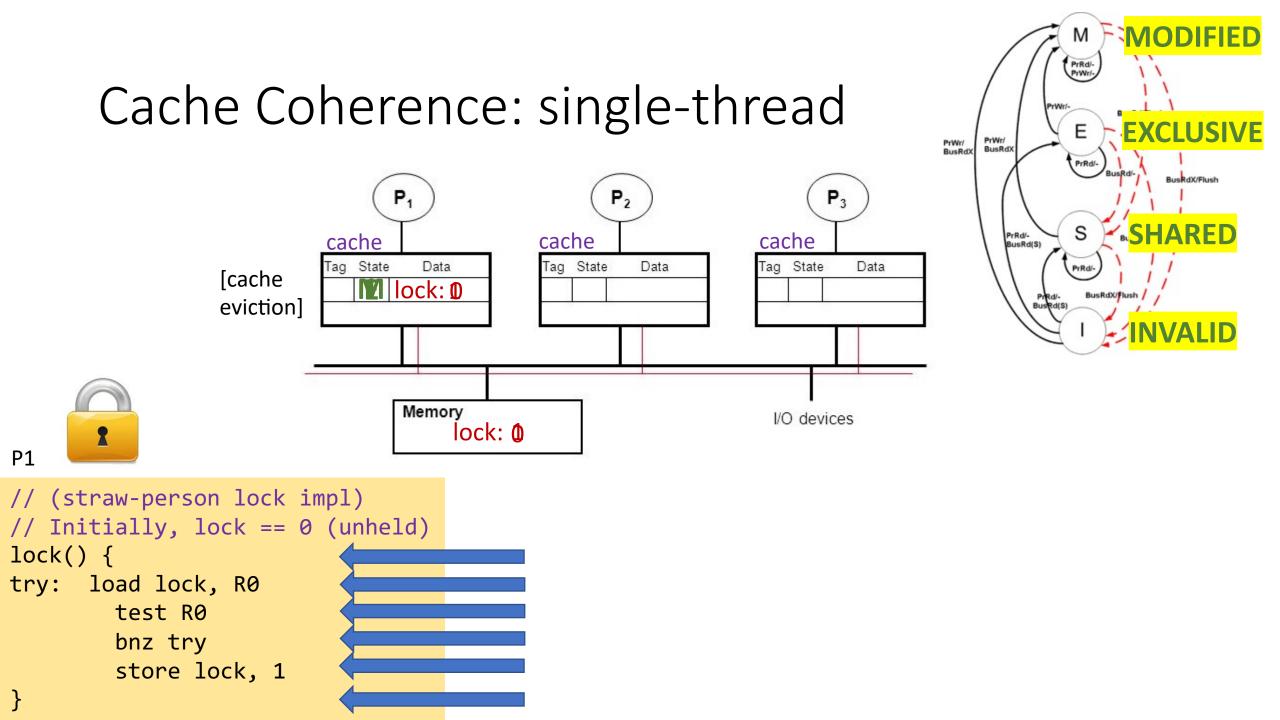

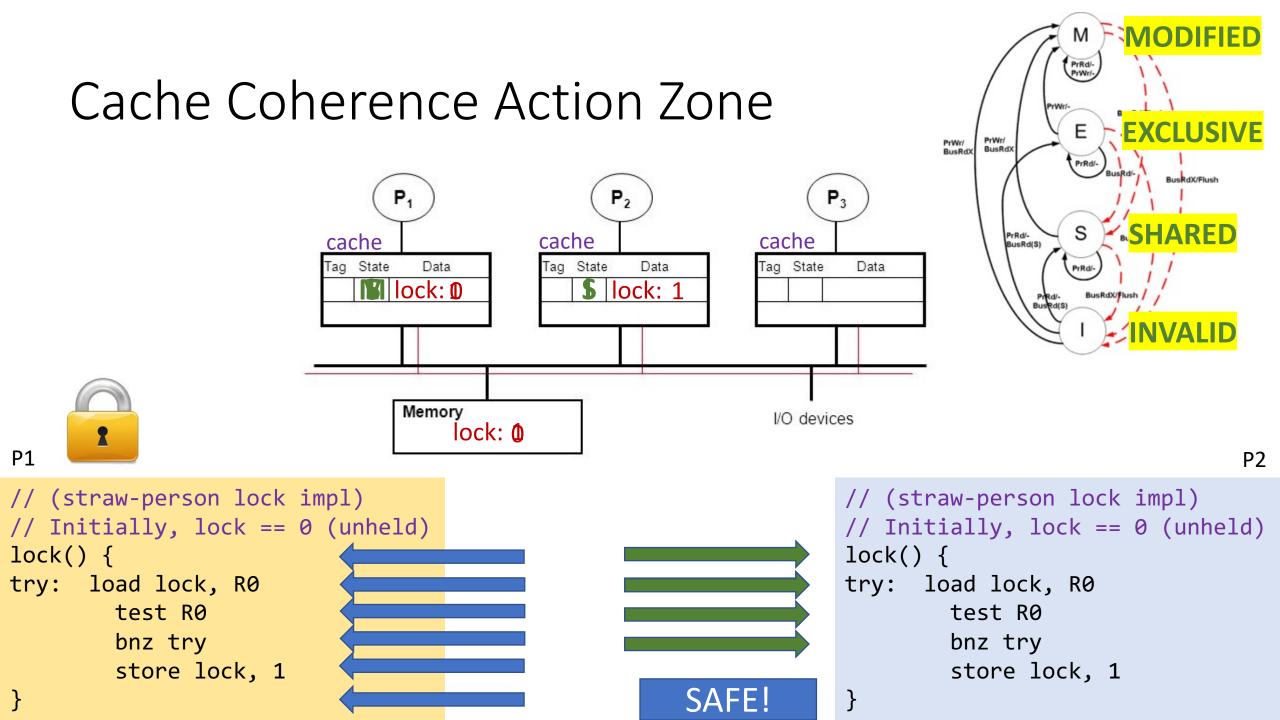

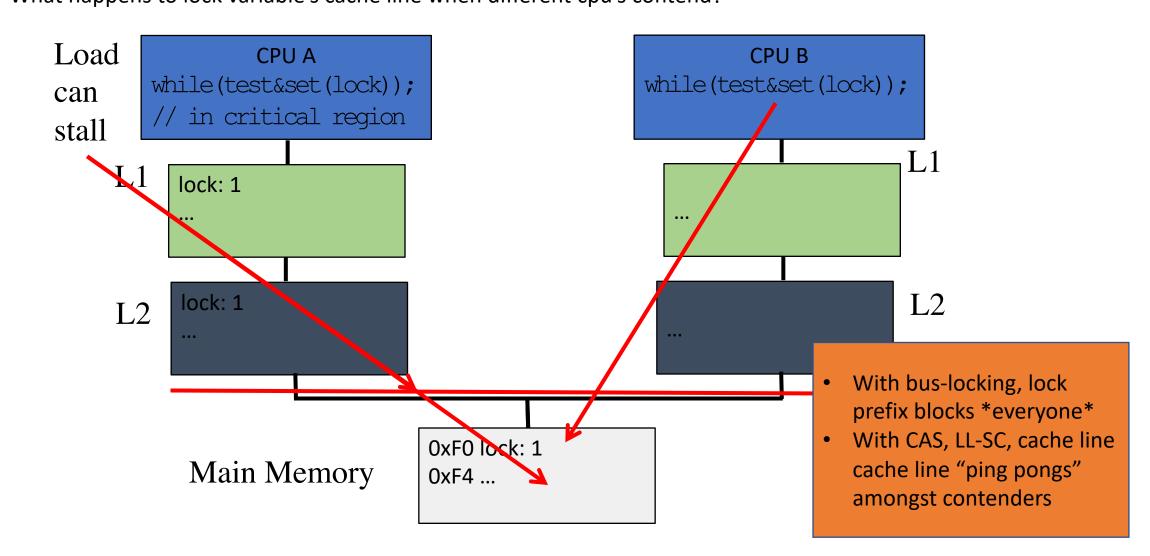

# Test & Set with Memory Hierarchies

Initially, lock already held by some other CPU—A, B busy-waiting What happens to lock variable's cache line when different cpu's contend?

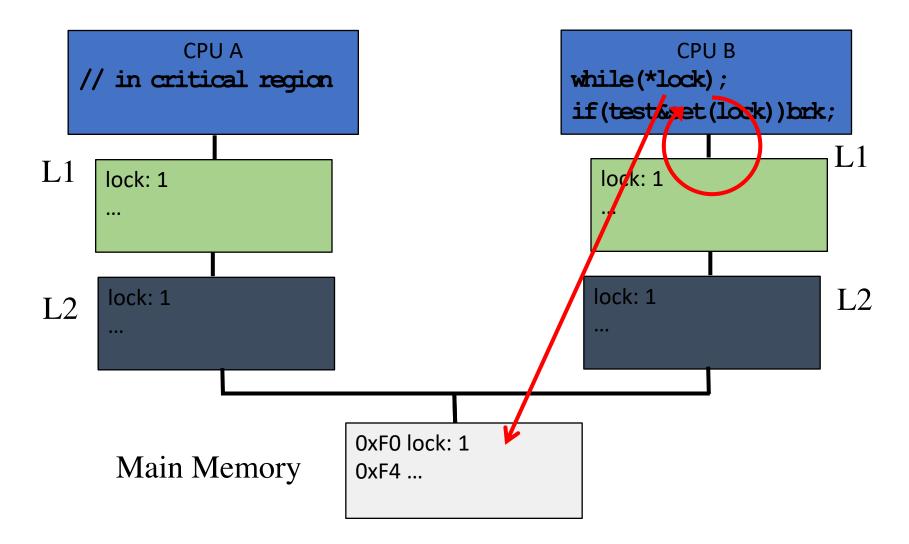

#### TTS: Reducing busy wait contention

```

Test&Set

Test&Test&Set

Lock::Acquire() {

Lock::Acquire() {

while (test&set(lock) == 1);

while(1) \{

while (*lock == 1); // spin just reading

if (test&set(lock) == 0) break;

Busy-wait on cached copy

Busy-wait on in-memory copy

Lock::Release() {

Lock::Release() {

*lock = 0;

*lock = 0;

```

- What is the problem with this?

- A. CPU usage B. Memory usage C. Lock::Acquire() latency

- D. Memory bus usage E. Does not work

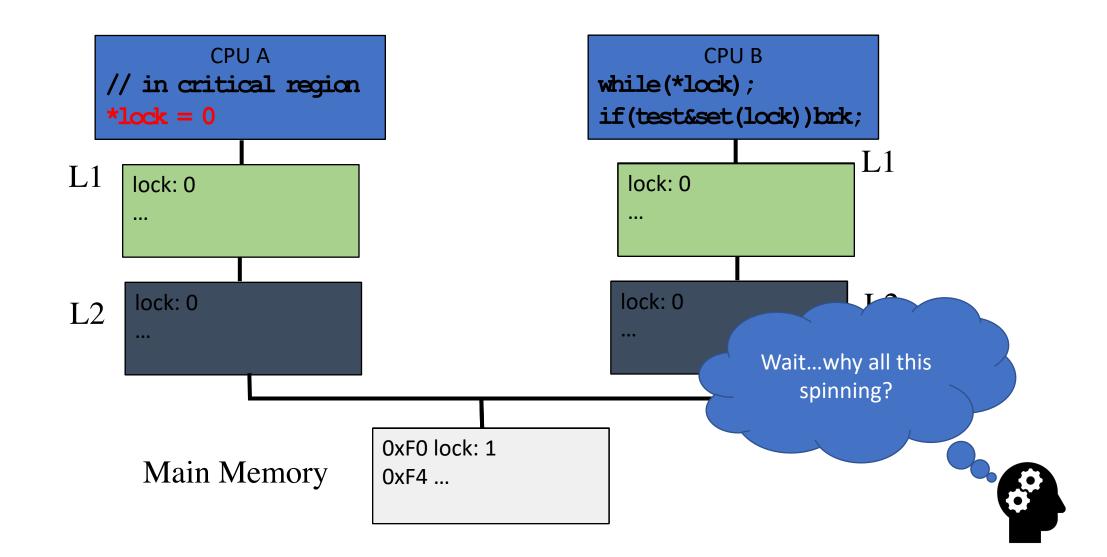

# Test & Test & Set with Memory Hierarchies

What happens to lock variable's cache line when different cpu's contend for the same lock?

## Test & Test & Set with Memory Hierarchies

What happens to lock variable's cache line when different cpu's contend for the same lock?

#### How can we improve over busy-wait?

Lock::Acquire() {

while(1) {

while (\*lock == 1) ; // spin just reading

if (test&set(lock) == 0) break;

}

#### Mutex

- Same abstraction as spinlock

- But is a "blocking" primitive

- Lock available  $\rightarrow$  same behavior

- Lock held  $\rightarrow$  yield/block

- Many ways to yield

- Simplest case of semaphore

```

void cm3_lock(u8_t* M) {

u8_t LockedIn = 0;

do {

if (__LDREXB(Mutex) == 0) {

// unlocked: try to obtain lock

if ( __STREXB(1, Mutex)) { // got lock

___CLREX(); // remove __LDREXB() lock

LockedIn = 1;

else task_yield(); // give away cpu

else task_yield(); // give away cpu

} while(!LockedIn);

```

- Is it better to use a spinlock or mutex on a uni-processor?

- Is it better to use a spinlock or mutex on a multi-processor?

- How do you choose between spinlock/mutex on a multiprocessor?

## **Priority Inversion**

```

A(prio-0) → enter(I);

B(prio-100) → enter(I); → must wait.

```

Solution?

**Priority inheritance:** A runs at B's priority MARS pathfinder failure: <u>http://wiki.csie.ncku.edu.tw/embedded/priority-inversion-on-Mars.pdf</u>

Other ideas?

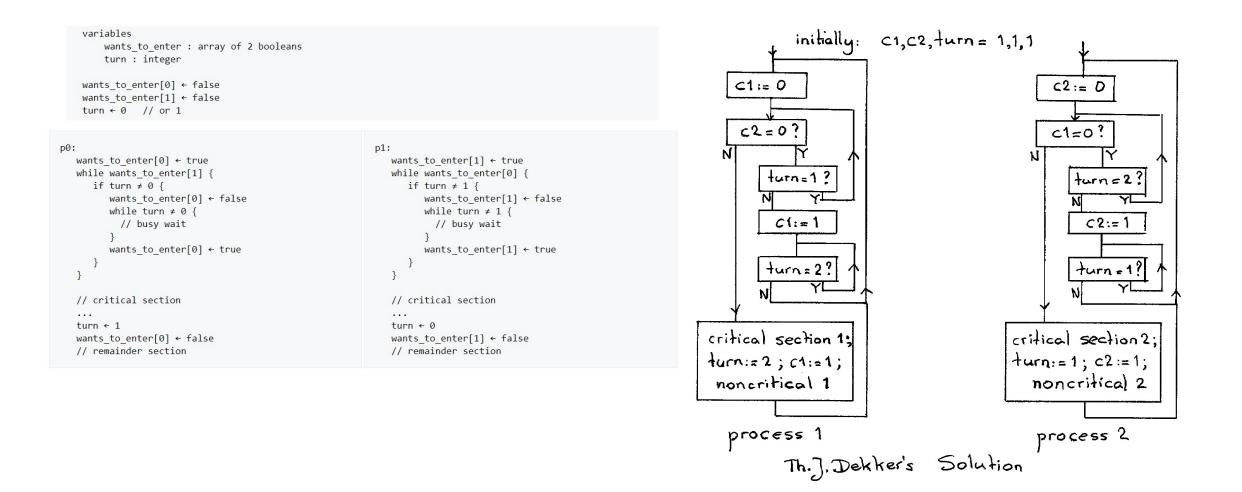

# Dekker's Algorithm

### Questions?